hello.

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

If you're functionally simulating your design for an Intel FPGA, you're likely using an EDA simulator. This time, we will introduce "NativeLink simulation" in the work flow. Hanako is also one push flow!

This time, we will introduce an example using Questa* - Intel® FPGA Edition (hereafter referred to as Questa-IFE, including Starter Edition) as a simulation tool.

What is NativeLink

Running EDA tools from Quartus® Prime is called NativeLink.

For example, when you click the Quartus Prime menu, <Questa - IFE starts, compiles and loads necessary for simulation, displays the simulation results in the waveform window>, and so on automatically.

This flow is highly recommended not only for those who do not know the GUI operation of Questa - IFE but also for those who want to improve the work efficiency of their operations.

Hanako's Tweet

If my design contains Intellectual Property (IP) modules created with IP Catalog or Platform Designer, how do I know which simulation library to use for my simulation tool?

NativeLink simulation eliminates such worries!

This method will automatically load all the simulation libraries needed to functionally simulate the IP module.

NativeLink Supported Environments

The environments in which NativeLink can be used are shown below.

| Table 1. NativeLink supported environment(*1) | |

| handle Quartus Prime |

Quartus Prime Standard Edition / Quartus Prime Lite Edition * Pro Edition is not supported (For Pro Edition, please refer to this content.) |

|

to support |

Aldec Active-HDL / Riviera-PRO Cadence Xcelium* Parallel Logic Simulation Siemens EDA ModelSim SE / Questa Advanced Simulator Siemens EDA Questa - Intel FPGA Edition Synopsys VCS / VCS MX |

Note 1: All schematic designs (.bdf) must be converted to HDL.

<Reference FAQ> Q: I want to simulate a design with a schematic in ModelSim, but it doesn't work.

Note 2: For the supported version of each EDA tool, please check the release notes for each version of Quartus Prime you are using.

Set up your environment

Set up your environment to run NativeLink.

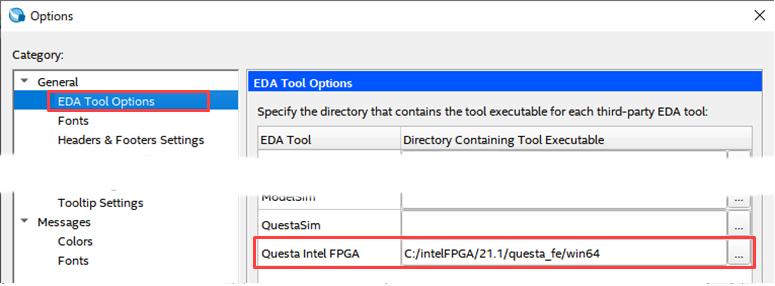

- Click EDA Tool Options under Tools menu ➤ Options ➤ General in Quartus Prime.

- Questa - Intel FPGA line Click the [...] button on the far right and specify the absolute path of the folder where the executable program is saved.

For Windows OS, specify the win64 folder where questasim.exe is saved.

work flow

- Register all the designs required for Quartus Prime compilation in the Quartus Prime project.

Project menu ➤ Add/Remove Files in Project

* In the case of designs that include IP, be sure to check Hanako 's Point ♪①/Hanako's Point♪②.

* If the design does not include IP,proceed to 2.

Hanako's point ♪ ①

If IP created inPlatform Designer is included

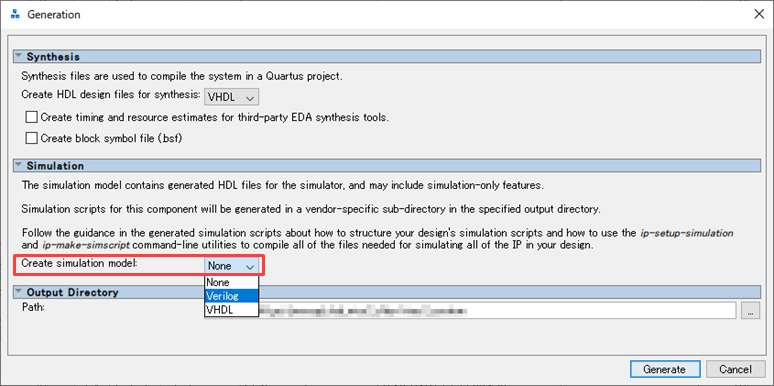

Enable the "Create simulation model option" in the Generation dialog Box that pops up when you run Generate HDL.

Clicking the Generate (or Generate HDL) button after selecting the language to generate will also generate a functional model for your simulation tool.

Hanako's point ♪ ②

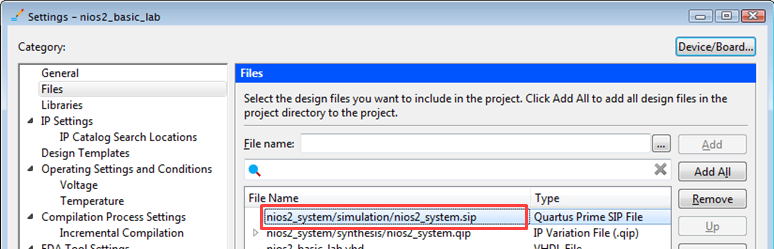

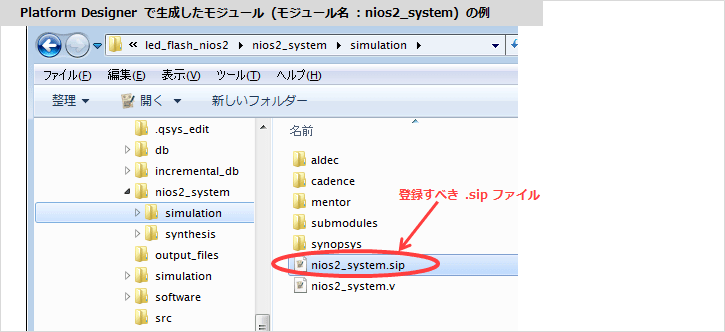

"IP module created with Platform Designer" or "IP module selected from IP Catalog and created with Platform Designer GUI base"

If it is included in your design, be sure to register <ip_name>.sip as well as <ip_name>.qip using the Quartus Prime menu below.

Project menu ➤ Add/Remove Files in Project

* "IP module created by MegaWizard Plug-In Manager based GUI by selecting IP from IP Catalog" does not generate *.sip file.

Register only the *.qip file in the project.

<Related FAQ> What kind of file is a .sip file?

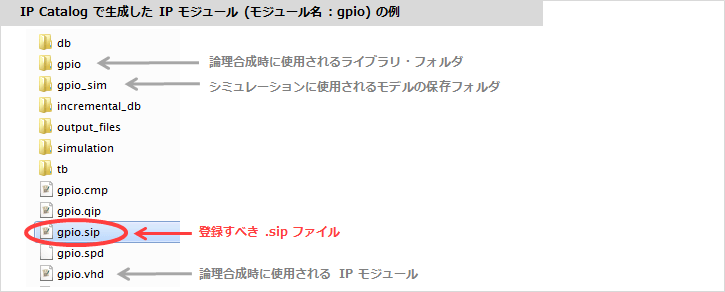

Where the .sip file is generated depends on whether you created the IP module in IP Catalog / Platform Designer.

[IP module created with IP Catalog]

A .sip file will be generated in the folder where the <ip_name>.v (or .vhd) was generated.

(* It is in the folder in the same hierarchy as the <ip_name>_sim folder.)

A .sip file will be generated in the <ip_name>. folder ➤ simulation folder.

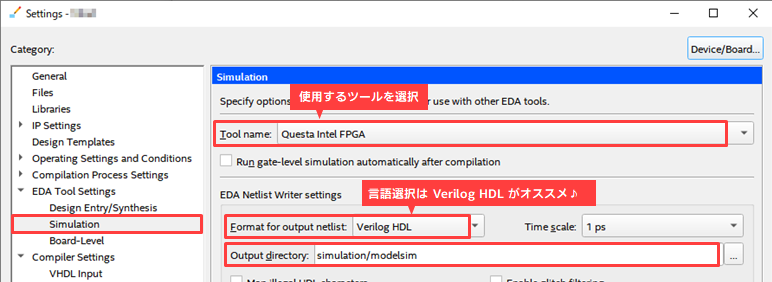

2. Select Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulation and set the following items in EDA Netlist Writer settings.

・ Tool name : Questa Intel FPGA (* Select this for Starter Edition as well)

・ Format for output netlist : Verilog HDL (reference: Hanako's point♪③)

・ Output directory: simulation/modelsim (default is recommended)

Hanako's point ♪ ③

Even if the simulation model and testbench when creating the IP are in VHDL, it is recommended to select Verilog HDL for this option.

This choice of language affects the vsim -L command in the NativeLink executable script.

In recent IP, even if VHDL is specified for the language selection of the simulation model, the lower model is often configured in SystemVeriog, which inevitably requires a simulation library for Verilog HDL. In that case, it is necessary to specify all libraries for Verilog HDL with the vsim -L command, so use Verilog HDL for Format for output netlist even if the model is generated in VHDL.

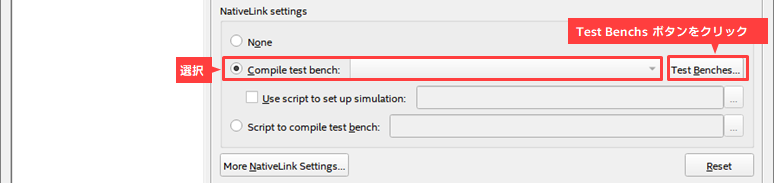

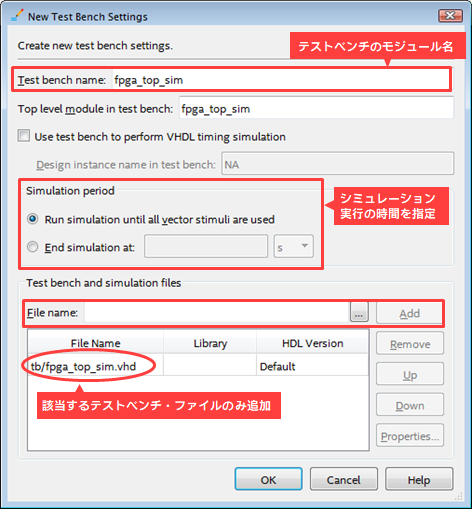

3. Register the testbench in the NativeLink settings.

Select Compile test bench and click the Test Benches button.

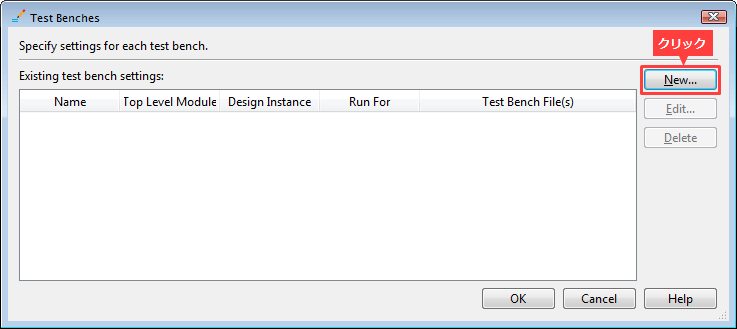

Click the New button in the Test Benches window.

Set the following items in the New Test Benches Settings dialog Box.

・ Test bench name: Enter the module name of the test bench (enter the Top Level module in test bench column at the same time)

・ Simulation period : Set the end time of simulation execution

・ File name : Click the [...] button on the right end and select the testbench file. Register with the Add button.

Close each window with OK to return to the Settings window.

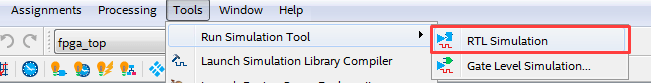

4. Perform function simulation with NativeLink!

Click Tools menu ➤ Run Simulation Tool ➤ RTL Simulation.

* Analysis & Elaboration or Analysis & Synthesis or Fitter process must be executed in advance to execute RTL Simulation.

However, do not run Start Compilation (Processing menu). EDA Netlist Writer automatically runningSisters

Scripts are not generated for successful RTL Simulation.

(If you have run a full compile, run Analysis & Elaboration or Analysis & Synthesis again, or run the Fitter again.

Do RTL Simulation. )

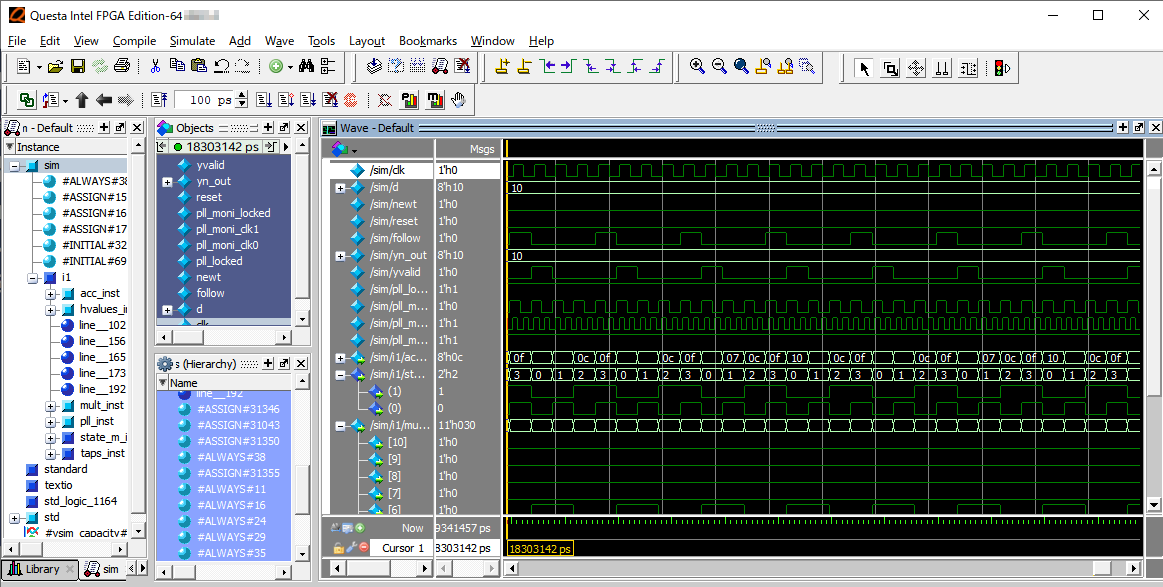

Questa - Compile in IFE, apply library, load, add signal to Wave window and run simulation. All these operations are automatically performed and the waveform is displayed in the Wave window.

Users only need to check the Wave window! How efficient!

By all means, please try to perform function simulation with NativeLink.

Click here for recommended articles/materials

Let's monitor internal signals of Intel® FPGA by simulation <Questa* - Intel® FPGA Edition>

Let's monitor the internal signal of Intel® FPGA by simulation <Testbench description>

Intel® FPGA Development Flow/FPGA Top Page