It has a wealth of functions useful for verification, and we will introduce waveform comparison, which is one of the verification functions.

Waveform comparison

Waveform comparison function

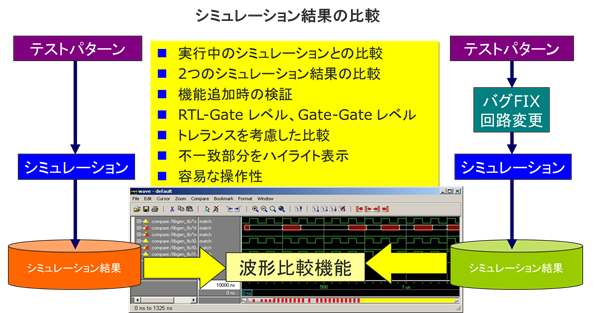

The waveform comparison function allows you to compare two simulation results.

For example, it is possible to compare the simulation results before and after a circuit change such as a bug fix, and check the effect of the fix on the operation. The waveform comparison function highlights discrepancies in the simulation results for easy judgment.

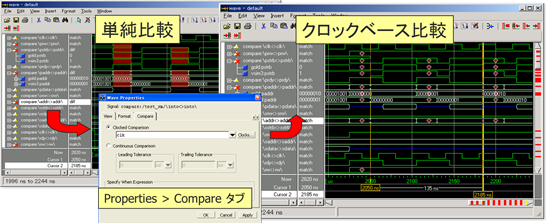

(1) Supports two comparison modes

● Simple comparison

Compares the value of the selected signal when it changes. You can set comparison conditions such as giving a tolerance (allowable error) time to the signal to give it width, or comparing waveforms only when enabled.

● Clock-based comparison

Compare according to the edge of the reference clock. You can give the reference clock an offset time.

(2) Compare signal waveforms between layers or with different signal names

When comparing "hierarchical RTL design" and "logic-synthesized flat design", the waveforms cannot be compared simply because the hierarchy and signal names do not match and the bus is divided, but the waveform comparison of Questa Sim / ModelSim is , change the hierarchy of the reference design to be compared, add signal names, and automatically reconstruct the decomposed bus signals.

(3) Ability to set matching rules for signal strength to be compared

There are four types of match conditions: “0”, “1”, “X”, and “Z”, and the matching signal strength can be set for each.

View comparison results

Shown below is an example of the comparison result in simple comparison.

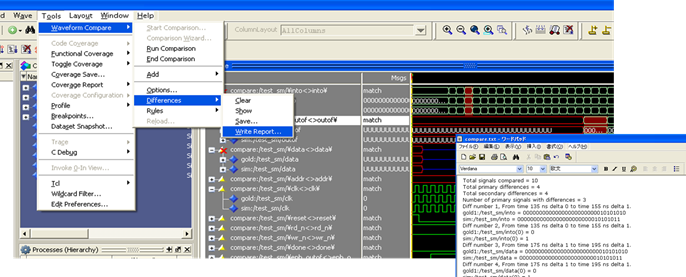

Waveform comparison report output

You can output the comparison result to a file. The following is an example of saving discrepancies in text.

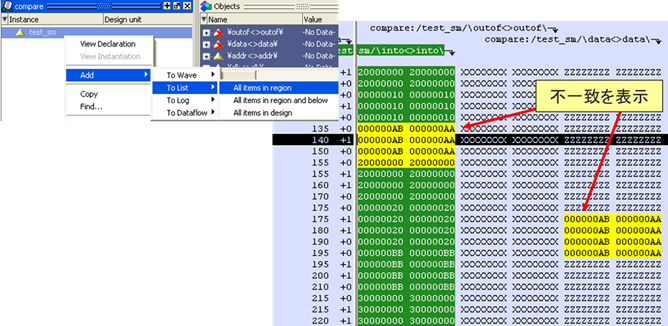

Show Comparison Results in List Window

Displaying discrepancies in a list window provides detailed comparisons as well as text output. The following is an example of displaying mismatch information in the list window.

Validation with waveform comparison

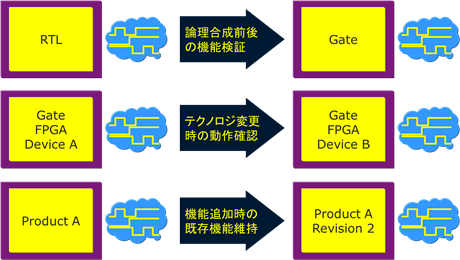

Verification where waveform comparison is useful might look something like this:

(1) Comparison between RTL and Gate

Example of use: Perform logic comparison between synthesized netlist or hand-corrected netlist and original RTL. It is convenient to use when you manually modify the RTL to remove test circuits, reduce circuit area, improve performance, or improve visibility.

(2) Gate-to-gate equivalence verification when technology is changed

Example of use: Logical comparison between FPGA netlist for prototype and ASIC netlist for mass production, logical comparison when changing from other company's FPGA design to IntelFPGA design.

③ Confirmation of maintenance of previous function when circuit function is changed

Usage example: There are many cases where bugs are overlooked due to the preconceived notion that unaffected signals do not change. "Waveform comparison" can be used to confirm that signals that do not affect circuit modifications do not affect others.

Related Information

▶ assertion validation

▶ code coverage

▶ Waveform comparison

▶ Enhanced dataflow

Seminar/Workshop

▶ [Online Seminar] Assertion Validation with ModelSim <Free>

This seminar introduces the effects of assertion-based verification (ABV), code coverage, and extended data flow, which are debugging functions of Questa Sim / ModelSim. In particular, assertion-based verification is the preferred verification technique, utilized in more than half of FPGA designs.

▶ Related events and seminars

Inquiry

Manufacturer information Top

If you would like to return to the manufacturer information top page, please click below.

Trademarks and registered trademarks owned by Siemens: here