Overview of Altera SoCs for Embedded Systems

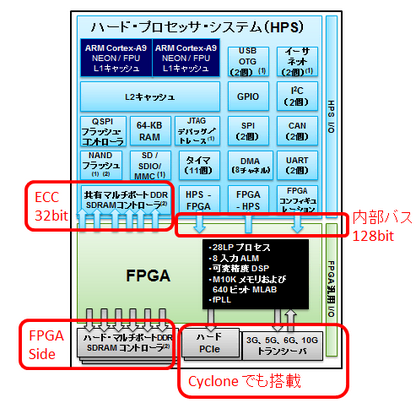

Altera's new product "Altera SoC" is a hard processor system (HPS) consisting of a dual-core ARM® Cortex™-A9 MPCore™ processor, a memory controller, and a rich set of peripherals, and a 28nm FPGA fabric (Cyclone® V and Arria® V). A high-bandwidth interconnect is used to connect between the processor system and the FPGA.

ARM-based SoCs are user-customizable and combine the performance and low power consumption of hard IP with the flexibility of programmable logic and the benefits of the powerful software ecosystem of the ARM architecture.

Altera SoC Features

The system architecture of the Altera SoC provided by Altera is as follows and has various features.

|

|

|

|

|

|

5 Reasons to Design with Altera SoCs

Reduced board size

Minimize board size and complexity by reducing the number of devices on the board by integrating FPGA, microprocessor, and DSP functions on a single chip

Reduced power consumption

Altera SoC allows you to take advantage of Altera's optimized 28nm Low-Power (28LP) process technology, rich hard IP and low-power serial transceivers

Reduce total system cost

必要なディスクリート・デバイス、電源レール、およびオシレータの数が少なくてすむため、部品 (BOM) コストの削減を実現

Design with FPGA flexibility

Quickly build a custom ARM processor system by choosing the best IP cores. In addition, flexible FPGA fabric supports changing industry standards and market demands. In addition, you can quickly develop custom hardware designs using the Quartus® II development software and Qsys system integration tools

Common development tools

Leverage ARM's strong ecosystem of software development tools, operating systems and middleware

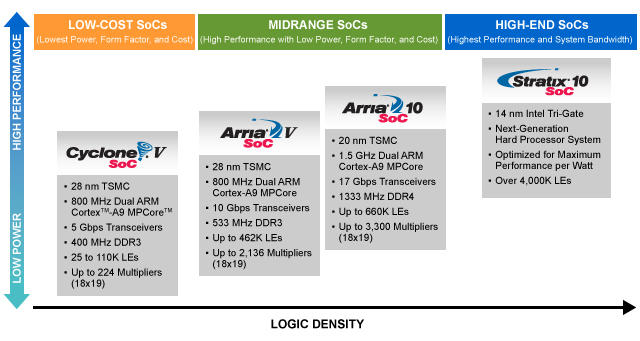

Further Expanding 28nm FPGA Portfolio

Altera offers a complete 28nm device portfolio to suit your diverse design requirements.

SoC FPGAs expands on the extensive Cyclone V SoC FPGA and Arria V SoC FPGA families. Each device family is differentiated by part number by optimizing requirements for performance, I/O resources, package size, power consumption and cost.

Start software development today

With the Altera SoC FPGA Virtual Target (Virtual Target), a fast functional simulation of SoC hard processor systems and board-level components, you can start developing application software for your SoC today. SoC Virtual Target provides unparalleled control and visibility into software, enabling greater debugging capabilities for complex multi-core processor-based embedded systems.