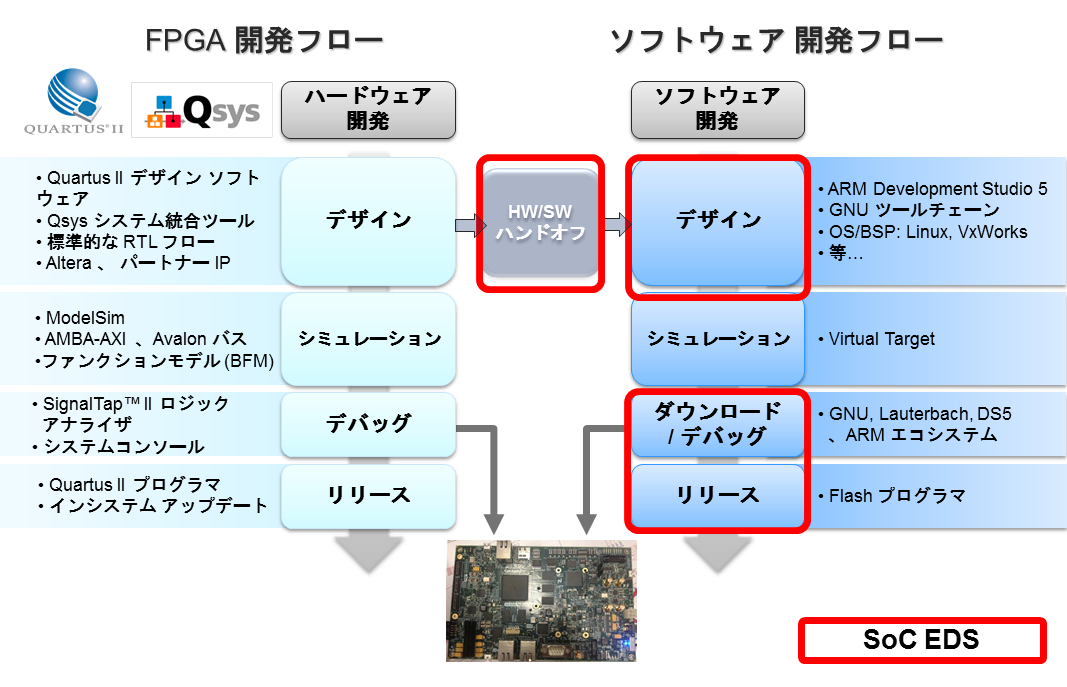

The Intel® SoC Embedded Design Suite (EDS) provides the following development tools that enable you to develop firmware and application software on the Intel SoC hardware platform.

Development tools provided by Intel SoC EDS

|

|

|

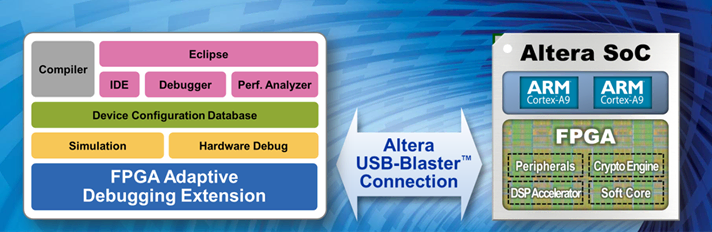

Industry's First FPGA Adaptive Software Toolkit: ARM Development Studio 5 (DS-5) Altera Edition

The ARM DS-5 Altera Edition Toolkit is provided under an exclusive agreement with Intel as part of the Intel SoC Embedded Design Suite (EDS).

Combining the system development-ready ARM DS-5 tool suite with Intel SoC devices, this toolkit gives embedded developers an unparalleled level of visibility and control across the chip.

Features of the DS-5 Altera Edition

| Non-intrusive tracing |

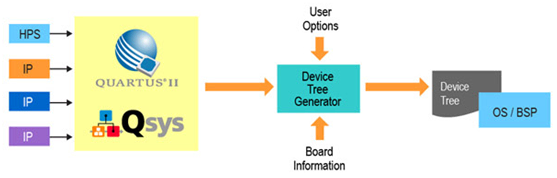

Hardware/software handoff

Intel's hardware/software interface utilities enable hardware and software teams to work independently and use their own familiar design flows.

These utilities generate interface files for software design flows from Quartus® II output files. A utility program generates a device tree.

A device tree is an industry standard way of describing hardware to an operating system (primarily Linux).

Specify the hardware corresponding to the board and FPGA configuration so that the corresponding driver is loaded when the kernel is launched.