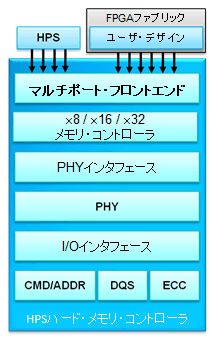

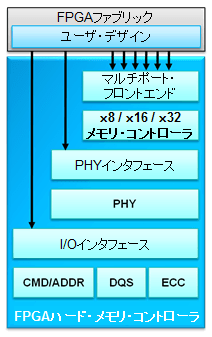

The SoC FPGA has a hard memory controller.

This memory controller supports ECC (Error Correction Code) on both HPS (Hard Processor System) and FPGA side.

Due to the increase in soft error rates, many designers are starting to consider adding error correction code (ECC) to external DDR memories.

ECC can be used to correct single-bit errors, greatly reducing the possibility of system failure.

Intel® SoC FPGAs are the perfect devices to support ECC.

By integrating all the necessary logic functions, ECC for external memory can be achieved simply by increasing the width of the DDR memory.

HPS Multiport Memory Controller Features

|

|

|

Features of FPGA Multiport Memory Controller

|

|

|