HyperLynx DRC は、問題を引き起こしそうな PCB 設計個所を特定してくれるデザイン・ルール・チェッカーです。デザイン・チェックを自動化して、検証工数を削減できます。

We regularly hold seminars on this product. Click here to apply!

Introduction video

<Environment construction>

Click here to download and install HyperLynx.

▶ How to download the Siemens EDA tool

▶ How to install HyperLynx

<Application for evaluation license>

If you do not have a license and would like to try out HyperLynx DRC, please contact us to request an evaluation license.

▶ Inquiries (request for evaluation license), etc.

Please write "I would like an evaluation license". The person in charge will contact you.

Functional overview

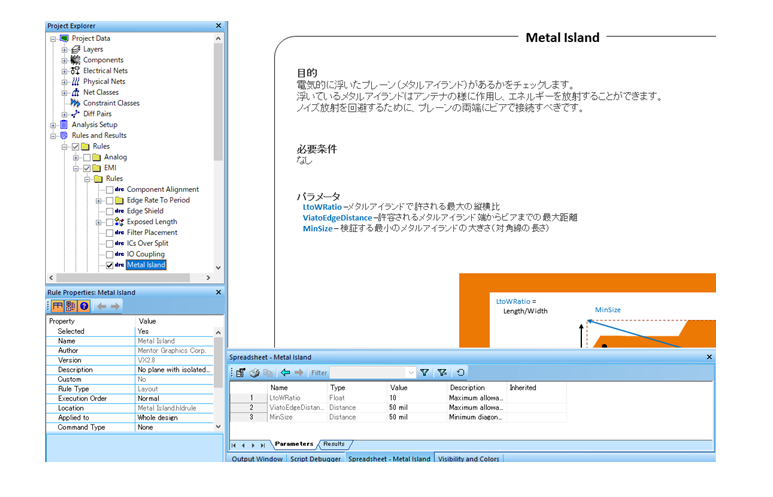

HyperLynx DRC can import files generated from PCB layout systems such as CAD tools and perform basic design rule checks as well as design rule checks to avoid EMI/EMC issues. increase. It prevents visual check errors and is not affected by the experience and knowledge of the person in charge of design.

以下のような流れで、デザイン・ルール・チェックを実行して、結果を確認することができます。エラーがあった場合はエラーの原因を取り除き、このループを繰り返すことでデザイン精度を高めていきます。

① ボード・レイアウト

② デザイン・ファイルを HyperLynx DRC へインポート

③ デザイン・ルール・チェック

④ 結果をレポート

⑤ エラーをレイアウトに反映して修正

<HyperLynx DRC Product Lineup>

HyperLynx DRC has four product lines with different design rule checks available. HyperLynx DRC 301 can also perform design rule checking with custom rules created by the user.

● HyperLynx DRC PE

● HyperLynx DRC 101

●HyperLynx DRC 301

●HyperLynx DRC 401

HyperLynx DRC comes preloaded with many standard rules and supports features to facilitate design rule checking.

Please see below for the corresponding rules for each product.

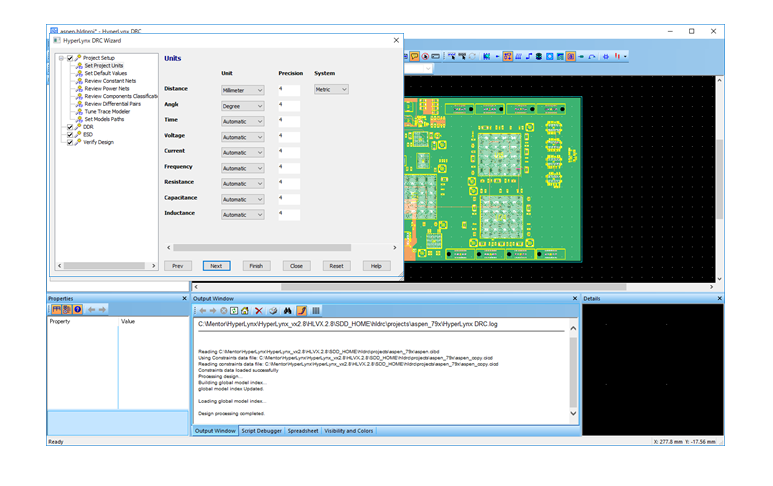

Startup and project setup

Open the board design data and make various settings for performing the design rule check.

Verification of design data

After loading your design, it is important to verify that the HyperLynx DRCs correctly recognize your design data. Make sure you know your design components and stackup data correctly.

If the contents of the object list are incorrect, the rule cannot produce accurate results.

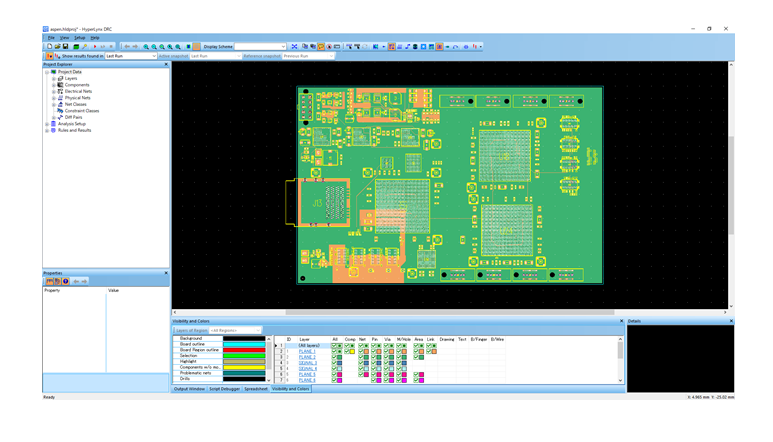

Run Design Rule Check

It is important to limit the number and scope of rules that are executed to avoid a large number of violations (such as spurious errors). Then gradually add more rules to expand their scope.

In other words, it is important to check whether the target and content of the design rule check are appropriate before execution. If the target and content are not properly specified (restricted), a huge number of pseudo-errors will occur. increase.

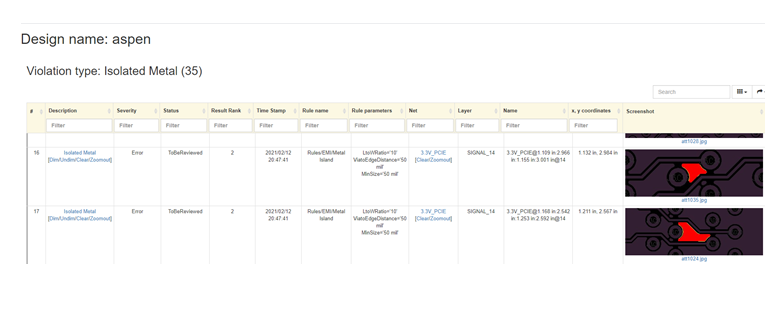

Documenting rule violations

After running a design rule check, you can save the results and easily document them.

Also, outputting in CSV format makes it easier to use with third-party tools. It is also possible to export a ShareList.

Related Information

Seminar/Workshop

FPGA board design methodology aiming for zero revisions

Shortening the time required for checking circuit board drawings and reducing the burden on engineers

▶ Siemens EDA Seminar

Inquiry

If you have any questions regarding this article, please contact us below.

Manufacturer information Top

If you would like to return to the manufacturer information top page, please click below.

Trademarks and registered trademarks owned by Siemens: here