Overview

High-frequency switches using wide bandgap semiconductors contribute to the efficiency of power conversion. Silicon carbide switches, for example, can be implemented as SiC MOSFETs or as SiC FETs in a cascode configuration.

This article traces the origins of SiC FETs, their evolution to the latest generation, and compares their performance with other technologies. In four installments, I will discuss the differences in physical characteristics, approaches and features for ideal switches, reliability, and unique uses in real-world applications.

SiC FETs – an alternative approach

With the advent of wide bandgap technology, many semiconductor manufacturers have chosen to develop SiC MOSFETs using their existing production lines, while others are starting from a blank slate and considering other options. did. The simplest switch using SiC is the JFET structure, which has no gate oxide and is a unipolar conduction device, so it does not have the limitations of MOSFETs.

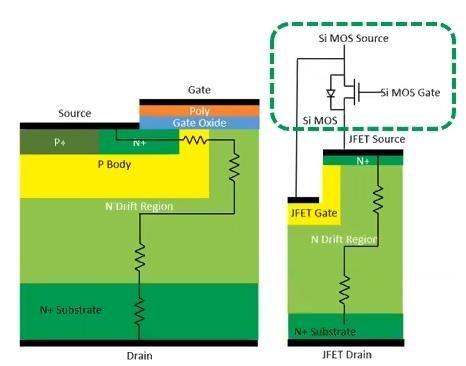

However, this device has a major drawback. It is "normally on" when the gate drive is 0V and requires a negative drive to turn it off. This is inconvenient, especially in transient situations such as system on/off, and in the worst case leads to application failure. A SiC FET is a combination of a SiC JFET and a silicon MOSFET that is normally off but maintains the advantages of a JFET over a MOSFET. Figure 1 compares the layout of a SiC FET (right) and the circuit diagram of a typical SiC MOSFET (left).

The arrangement of SiC FETs is called a cascode, and may be familiar to adult engineers who have seen prototypes of vacuum tube combinations aimed at noise reduction in audio amplifiers. Cascode or "emitter switches" have come in many forms over the years, including bipolar transistors and BJT and MOSFET combinations, but the common feature is that a low voltage switch controls a high voltage switch and a high voltage It is a good balance between rating and ease of driving. However, circuits using BJTs were not popular for high power due to their large base drive current and slow switching speed. SiC cascodes, or "SiC FETs," have solved these problems.

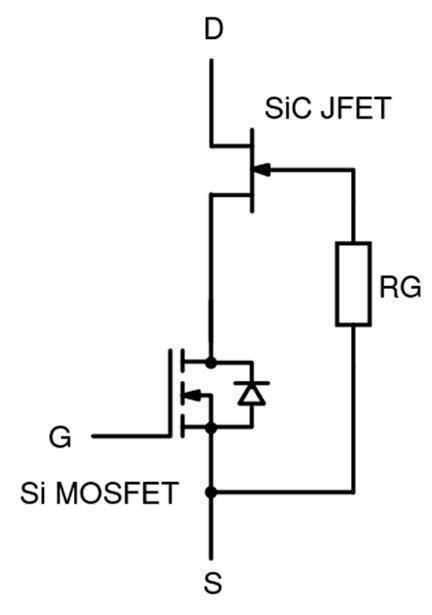

Referring to the schematic of the SiC FET in Figure 2, when the Si-MOSFET is turned on through the gate, the source and gate of the JFET are effectively shorted, causing the JFET to conduct. At this time, the on-resistance of the low-voltage Si-MOSFET can be much smaller than that of the high-voltage SiC FET, so the current flow between the drain and source of the JFET and the MOSFET is fixed while the conduction loss of the JFET is fixed. will flow. When the Si-MOSFET is turned off, the JFET source voltage rises and exceeds the gate-source threshold (a few volts negative), turning off the JFET. Dynamically, the Si-MOSFET voltage remains low because of the device capacitance ratio.

SiC FETs have many advantages over SiC MOSFETs, both in terms of electrical performance and practicality. As a switch, on-resistance is a major factor, but compared to SiC MOSFETs, SiC FETs feature extremely high electron mobility in the channel. In addition, since the channel density is also high, the on-resistance of SiC FET is 2 to 4 times higher than that of SiC MOSFET for the same area of dies. I can. Compared to silicon superjunction MOSFETs, you can get up to 13 times more die counts. Silicon carbide as a material is likely to always be more expensive than silicon, so increasing dross die per wafer is critical to the success of SiC FET technology. As we have seen, the metric for the viability of a die is the figure of merit, RDSA.

Another advantage is RDS*EOSS, the trade-off between on-resistance and the output switching energy of the device, given by the output capacitance. This is a useful metric because paralleling more cells in a die can reduce on-resistance and conduction losses. However, not only does the area increase, but the capacitance directly increases, resulting in an increase in EOSS, which leads to increased frequency-dependent switching losses. Therefore, smaller values of RDS*EOSS are advantageous.

The SiC FET gate is the same as the cascaded Si MOSFET gate. As such, it can be easily driven at 12V or 15V with a large margin up to the absolute maximum of 25V for full enhancement and low RDSON. In addition, SiC FET gate drives are nominally compatible with silicon MOSFETs and IGBTs, ensuring backward compatibility when design upgrades to existing products. In practice, SiC MOSFETs and GaN HEMT cells require custom drive schemes for optimum efficiency and adequate protection against overvoltages on the gate.

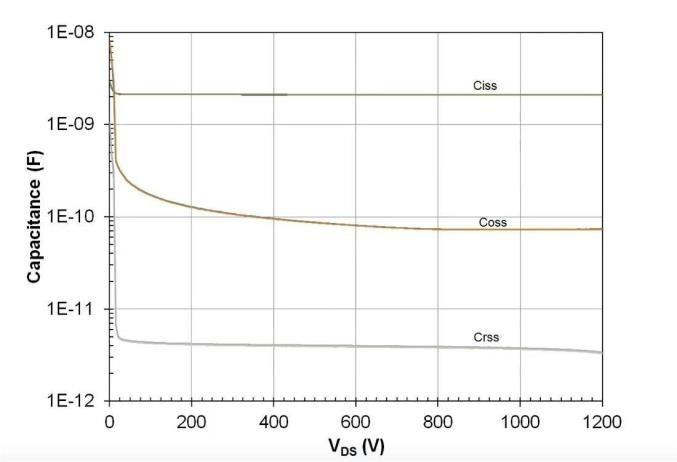

SiC FETs have very little gate-drain or "mirror" capacitance Crss and very fast switching due to the small device dimensions and the isolation effect of the cascode-arranged Si MOSFETs. In addition, the output capacitance COSS and the accompanying switching energy EOSS are also small, realizing high-speed switching with minimal loss. Due to their very fast edge rates, practical circuits require slow SiC FETs to reduce voltage overshoot and EMI. This can be done by adding a gate resistor, but at high switching frequencies a simple RC snubber is often a better solution as it introduces unacceptable control delays. Capacitors are usually set to about 3×COSS, which minimizes losses in series resistance. Figure 3 shows the capacitance of a typical SiC FET device and the change in drain voltage under blocking conditions. The calculation formula for each capacitance value is as follows.

・Ciss = CGS + CGD

(CDS is short)

・Crss = CGD

・Coss = CDS + CGD

SiCFET "body diode"

Power converters require perfect switches to conduct in both directions with low loss. This is a practical requirement in circuits such as AC motor drives and converters with inductive loads, the so-called "third quadrant" operation. IGBTs cannot do this, so a parallel diode is required, but silicon or SiC MOSFETs and JFETs conduct in either direction through the channel by controlling the gate.

Also, MOSFETs have a built-in body diode, which JFETs do not, and in hard-switched converters with inductive loads, this body diode is "dead-time" before the device's channel turns on through the gate. "Rectification" automatically conducts the current, allowing the current to flow in the opposite direction. This conduction accumulates a charge Qrr which is subsequently recovered when the body diode is reverse biased.

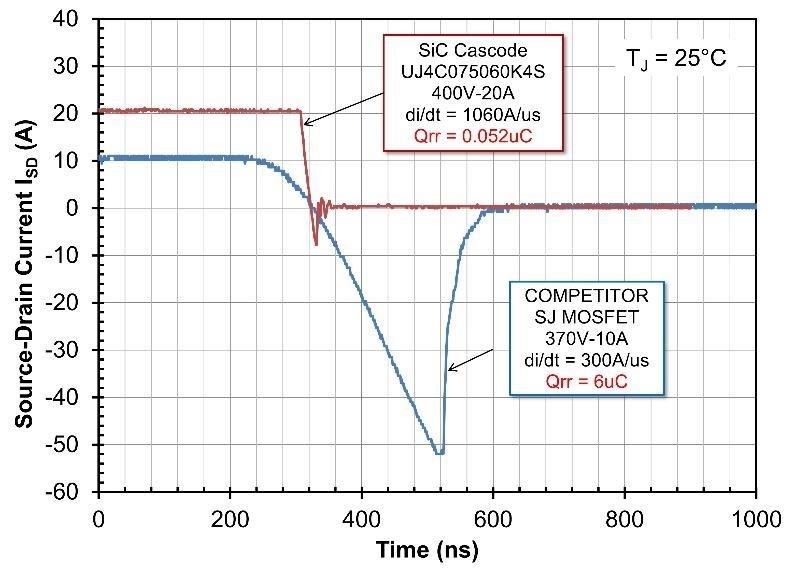

This behavior results in high peak power consumption, higher average values and lower efficiency at higher frequencies. This effect is extremely large in silicon-based MOSFETs, and in some cases they cannot be used practically in circuits that operate in CCM (Continuous Conduction Mode), such as general totem-pole PFC stages. SiC MOSFETs have a Qrr value of about 10 times that of Si, but SiC FETs are even better because of the lower device output capacitance and less stored charge in low voltage MOSFETs. Although the comparison depends on the voltage class of the device, Figure 4 is a typical reverse recovery plot for SiC FETs and similar silicon superjunction MOSFETs.

Although SiC MOSFETs and GaN devices have sufficiently low or no reverse recovery losses, the voltage drop due to reverse conduction is something else. This causes large losses during the dead time of the power converter. Si superjunction MOSFETs typically exhibit a diode drop of around 1V, and SiC MOSFETs are even worse as they have body diodes that easily drop 4V. A GaN HEMT cell in 3rd quadrant operation drops a voltage Vsd that is the sum of the I*R channel voltage and the gate threshold voltage minus the gate source voltage. The formula for calculating Vsd is:

・Vsd = (Vth-Vgs) + (Isd*Ron)

GaN gate threshold is typically 1.5V, so the total drop is large at high currents. In general, driving the gate negative to turn it off adds this voltage Vgs to the source-drain drop, resulting in a Vsd of several volts, significantly worse than other techniques. There is a possibility. SiC FETs also experience an I*R drop due to channel resistance when conducting source-drain, similar to GaN devices, but this drop is across the body diode of the low-voltage cascaded Si MOSFETs. It only increases with voltage and is relatively low. The resulting forward voltage drop is typically around 1.5V, better than the performance of SiC MOSFETs and GaN.

Inquiry

If you have any questions regarding this article, please contact us below.

Qorvo manufacturer information top page

If you want to return to Qorvo manufacturer information top page, please click below.