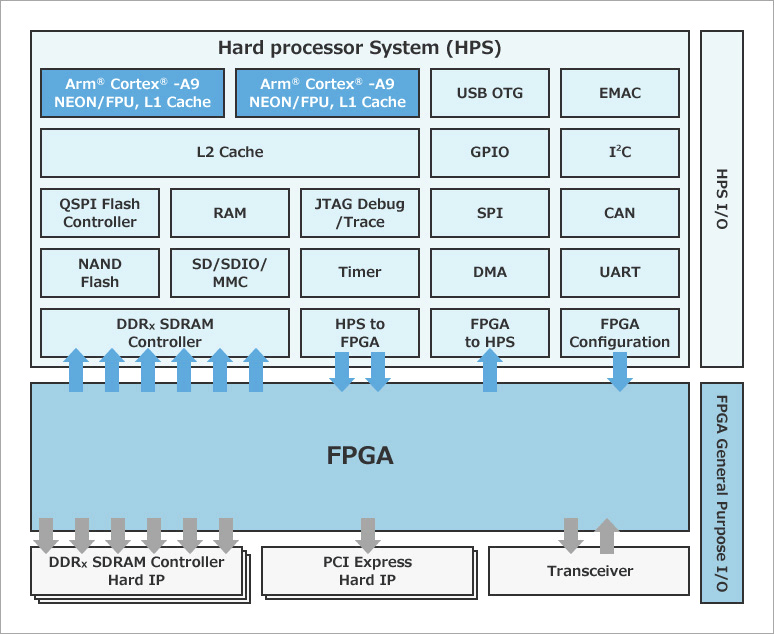

Intel ® SoC FPGA is a hard processor system (HPS) with an Arm ® Cortex ® processor microprocessor unit (MPU), consisting of a rich set of peripherals, a multiport memory controller, and an FPGA fabric device.

This page is the most suitable information for users using SoC FPGA.

SoC FPGAEcosystem Partner Links

Intel® and our ecosystem partners offer a wide range of choices for each SoC FPGA development need.

In addition to open source Linux, many commercial operating systems are available.

Also available are specialized development tools including a JTAG debugger and instruction trace capabilities.

1. What are SoC FPGAs?

Simply put, it's an Arm ® processor with a memory-mapped FPGA as one of its peripherals. An SoC FPGA is a product that integrates the HPS fabric, which consists of the Arm ® processor, peripherals, and memory interfaces, with the FPGA fabric into a single chip. SoC FPGAs enable fast time-to-market, low power consumption, low cost, reduced design risk, and smaller board size.

2. Tools Required for SoC FPGA Development

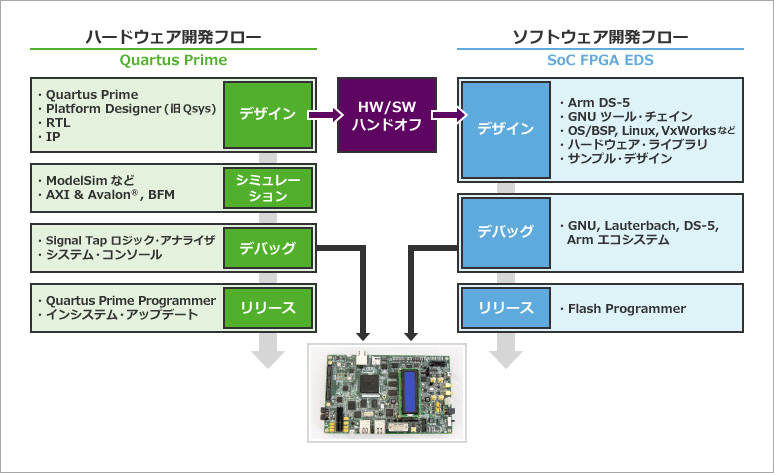

The SoC FPGA development flow can be divided into "FPGA hardware development flow" and "software development flow" as shown in the figure below.

2-1. FPGA hardware development flow

Use of FPGA development flow and design tools such as Intel® Quartus® Prime development software as a development environment, Intel® Platform Designer (formerly Qsys) system integration tool as a system configuration tool, ModelSim® simulator, and Signal Tap logic analyzer I can.

2-2. Software development flow

The Intel® SoC FPGA Embedded Development Suite (SoC EDS) is a comprehensive tool suite for embedded software development for Intel® SoC FPGAs.

Intel® SoC FPGA devices are also centered around Arm® processors, which are widely supported in the embedded software industry. Intel® and our ecosystem partners offer a wide range of choices for each development need. As for the operating system (OS), in addition to open source Linux, many commercial OSes are available.

For information handoff from hardware to software, use the hardware-to-software handoff utility included in SoC EDS. This utility generates handoff files for software design flows from output files generated by Quartus ® Prime and Platform Designer. This allows FPGA design teams and software design teams to follow their own design flows and work independently, increasing productivity.

3. SoC FPGA Document Public Site

3-1. Links to Intel® SoC FPGA related pages

|

Name |

Overview |

| Intel® FPGA Support Resources (Japanese page) |

Intel®_ Support resource entrance from this page |

| Intel® FPGAs & SoC FPGAs (Japanese page) |

Intel®_ The entrance of information by FPGA device from this page |

| Embedded Software and Tools for Intel® SoC FPGAs (Japanese page) |

This is the Tools and Software page. Quartus®, SoC EDS, DS-5 and other development tool information from this page |

| SoC FPGA Documentation page |

Various documents are available for target SoC FPGA devices.

|

| Hard Processor System (HPS) Register Address Map |

The Hard Processor System (HPS) register address map is published for the target SoC FPGA device. |

| Intel® SoC EDS Support Page (Japanese page) |

Intel®SoC EDS support page. We publish Documentation, Videos, Design Examples and Training Courses |

| Intel® Community | Intel ® Community is Intel®A wiki site aimed at providing community knowledge about FPGAs, technologies, tools, and their uses |

| Intel ® FPGA Knowledge Base (Japanese page) |

Tips and problem-solving methods for using Intel®FPGA products are published. |

3-2. Arm® related information

Arm ® related links are shown in the table below. For detailed information on Arm ® processors and peripherals, Arm ® genuine debuggers (Arm DS / DS-5™) and compilers (armcc), please refer to the following sites.

|

Name |

Overview |

| Arm ® Developer (document public site) | Cortex ®-A9, Cortex ®-A53, and other Arm ® CPU/peripheral/tool manuals can be found here |

| APS (beginner course) | Arm ® related technical information site. Cortex ®-A Beginner's Course, Embedded Linux Beginner's Course, etc. |

4. Intel® Content

4-1. Intel® SoC FPGA related design samples

● Various design samples for SoC FPGA are available.

|

Name |

Overview |

File / Web Page |

Corresponding board |

| SDMMC GSRD | The Golden System Reference Design (GSRD) provides key hardware and software system components that can be used as starting points for a variety of custom user designs. |

(Latest here) |

Arria ® 10 SoC Development Kits |

| QSPI GSRD |

(Latest here) |

Arria ® 10 SoC Development Kits | |

| SGMII GSRD |

(Latest here) |

Arria ® 10 SoC Development Kits | |

| NAND GSRD | (Latest here) | Arria ® 10 SoC Development Kits | |

| Remote debug | This example shows how to perform remote system debugging using the System-Level Debugging (SLD) tool. | Example Arria 10 | Arria ® 10 SoC Development Kits |

| HPS-to-FPGA Bridges | Implements a memory-mapped interface for hard processor systems (HPS) connected to the FPGA fabric. Run memory tests by reading/writing HPS memory using various ports on the HPS to measure data transfer performance. | Examples Readme Arria 10 Readme Cyclone V |

Arria ® 10 SoC Development Kits Cyclone ® V SoC Development Kit |

| PCIe root port | This reference design connects a PCIe Root Port running on the Arria ® 10 SoC development kit to a PCIe endpoint on the Cyclone ® V GT FPGA development kit or an endpoint on a commonly available Intel ® PCIe Ethernet adapter card. Thing. It is also applicable to Cyclone ® V SoC Development Kit and Arria ® V SoC Development Kit. | Examples | Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Secure boot | This document demonstrates how to implement the Intel Arria 10 SoC Secure Boot system using the Intel Arria 10 SoC FPGA Authentication Signing Utility tool to protect the first-stage bootloader image and a design example . | User Guide & Examples | Arria ® 10 SoC Development Kits |

| HPS DMA HWLIB | Demonstrates how to use the DMA API to initialize DMA and perform memory-to-memory transfers. | Example Arria 10 Readme Arria 10 |

Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| ECC HWLIB | Demonstrates on-chip RAM, SD/MMC, Quad Serial Peripheral Interface (SPI), DMA and Error Correction Code (ECC) API features for L2 cache. This example shows how to set up and enable ECC for each RAM, injection of single/double-bit errors, and how to set up interrupts for single/double-bit error detection. | Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

|

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| GPIO HWLIB | It shows how to use the General-Purpose Input/Output (GPIO) API to configure a GPIO as an output port to drive an HPS LED and a GPIO as an input port for an HPS pushbutton. | Example Arria 10 Readme Arria 10 |

Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| I2C HWLIB | Demonstrates how to read/write masters and slaves using the I2C API. This example demonstrates an LCD screen, I2C communication with EEPROM memory, and communication between two I2C modules. | Example Arria 10 Readme Arria 10 |

Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| Quad SPI HWLIB | Demonstrates how to use the Quad SPI API to perform Quad SPI reads/writes with common block I/O functions and data transactions using indirect and DMA modes. The example also demonstrates additional API features such as MMU and cache settings. | Example Arria V Readme Arria V |

Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Cyclone V Readme Cyclone V |

|||

| SD/MMC HWLIB | Demonstrates how to use the SD/MMC API to initialize an SD/MMC card and read/write using block I/O functions. | Example Arria V Readme Arria V |

Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Cyclone V Readme Cyclone V |

|||

| Timer HWLIB | Demonstrates how to use the Timer API for free-running timers, one-shot timers, watchdog timers, and global timer measurements. | Example Arria 10 Readme Arria 10 |

Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| Unhosted HWLIBs | It shows how to printf output using UART instead of semihosting. It also shows how to boot a bare metal program from an SD card. | Example Arria V Readme Arria V |

Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Cyclone V Readme Cyclone V |

|||

| SPI HWLIB | It shows how to use the SPI API to communicate between two SPI modules connected through the FPGA fabric. | Example Arria 10 Readme Arria 10 |

Arria ® 10 SoC Development Kits Arria ® V SoC Development Kit Cyclone ® V SoC Development Kit |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| HPS Peripheral Mapping to FPGA | This design example shows how to route the Hard Processor System (HPS) EMAC and I2C peripherals into the FPGA fabric and connect them to the FPGA I/O. | Examples Readme |

Cyclone ® V SoC Development Kit |

| Power Optimization HWLIB | Demonstrates the use of WFI or WFE calls to put the calling processor core into clock gating mode to save power. | Examples Readme |

Cyclone ® V SoC Development Kit |

| Shared Memory Partition | This design example shows how to configure and test memory protection rules for the Hard Processor System (HPS) SDRAM Controller. | Examples Readme |

Cyclone ® V SoC Development Kit Terasic Atlas SoC Kit |

● The Intel® FPGA Design Store page is a new page where you can search for Design Examples by setting conditions.

Links to various designs for SoC FPGA development kits

・ Designed for Intel Agilex ® 7

・ Design for Intel ® Stratix ® 10 SoC

●Embedded Software Developer Centeris customized for specific development roles listed below.

This page contains various materials and design examples.

For example, you can find links to materials such as the HPS SoC Boot Guide, which are difficult to reach from the device-specific pages above.

Pages that publish various materials and design examples customized for specific development roles

4-2. Intel® SoC FPGA related documents

Intel® The FPGAs & SoC FPGAs page is your gateway to finding documentation on FPGA and SoC products.

■ Introductory material

・ SoC FPGA Product Catalog (Japanese)

・ Design Considerations for SoC FPGAs Checklist (English)

4-3. Free SoC FPGA Online Training Course

the page below will show you the SoC FPGA related developer trainings published by Intel®.

5. Other content

5-1. RocketBoard.org community portal site

The RocketBoards.org community portal site provides information on Linux for SoC FPGAs.

- Various design samples are published on the Projects page of RocketBoards.org.

- Various documents are published on the RocketBoards.org Documentation page.

- Information about development kits (boards) provided by Intel® and partners is published on the RocketBoard.org Boards page.

For example, Macnica Mpression's Sodia board page has Japanese resources available, as well as various documents, reference designs, demos, etc.

5-2. Videos published on YouTube

On YouTube, various Various videos for Intel® SoC FPGAs is published.

6. Samples provided with SoC EDS

SoC EDS comes with Golden Hardware Reference Designs (GHRD) for SoC FPGA Development Kits, U-Boot, Linux and bare-metal reference examples for quick development. It is

SoC EDS v18.0 has Linux and bare metal examples in the examples/software folder, including:

|

Name |

Overview |

remarks |

| Altera-SoC FPGA-Blinking-LED-Linux-GNU | For Linux: LED blinking sample | For the Linaro Linux GCC compiler |

| Altera-SoC FPGA-HardwareLib-16550-CV-ARMCC | For bare metal: Cyclone ® V SoC + 16550 UART API usage example | for Arm® Compiler |

| Altera-SoC FPGA-HardwareLib-16550-CV-GNU | For bare metal: Cyclone ® V SoC + 16550 UART API usage example | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-ECCL2-CV-ARMCC | For bare metal: ECC API usage example in Cyclone ® V SoC L2 cache | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-ECCL2-CV-GNU | For bare metal: ECC API usage example in Cyclone ® V SoC L2 cache | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-FPGA-CV-ARMCC | For bare metal: Cyclone ® V SoC FPGA Manager API usage example | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-FPGA-CV-GNU | For bare metal: Cyclone ® V SoC FPGA Manager API usage example | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-SPI-CV-ARMCC | For bare metal: EEPROM read/write example using Cyclone ® V SoC SPI API | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-SPI-CV-GNU | For bare metal: EEPROM read/write example using Cyclone ® V SoC SPI API | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-Timer-A10-ARMCC | For Bare Metal: Arria ® 10 SoC Timer API Use Case | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-Timer-A10-GNU | For Bare Metal: Arria ® 10 SoC Timer API Use Case | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-Timer-AV-ARMCC | For bare metal: Arria ® V SoC Timer API usage example | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-Timer-AV-GNU | For bare metal: Arria ® V SoC Timer API usage example | for the GCC compiler |

| Altera-SoCFPGA-HardwareLib-Timer-CV-ARMCC | For bare metal: Cyclone ® V SoC Timer API usage example | for Arm® Compiler |

| Altera-SoCFPGA-HardwareLib-Timer-CV-GNU | For bare metal: Cyclone ® V SoC Timer API usage example | for the GCC compiler |

| Altera-SoC FPGA-HelloWorld-Baremetal-ARMCC | For bare metal: Hello World sample | for Arm® Compiler |

| Altera-SoC FPGA-HelloWorld-Baremetal-GNU | For bare metal: Hello World sample | for the GCC compiler |

| Altera-SoC FPGA-HelloWorld-Linux-GNU | For Linux: Hello World sample | For the Linaro Linux GCC compiler |

| Altera-SoC FPGA-Push-Button-Linux-GNU | For Linux: Push-Button sample | For the Linaro Linux GCC compiler |

Note: The Minimal Preloader (MPL) bare-metal sample Altera-SoCFPGA-HardwareLib-MPL is not included in SoC EDS Standard Edition version 18.0. If you use the MPL, you should use the samples that come with Standard Edition version 17.1. See the SoC EDS Release Notes page for details.

7. SoC FPGA Ecosystem (Partner Link)

SoC FPGA is Arm®Processor-based and Arm®Inheriting the strengths of the ecosystem. intel® and ecosystem partners offer a wide range of choices for each development need.

Detail is, Intel ® SoC FPGAs Ecosystem (Japanese page)Please refer to.

7-1. SoC FPGA Operating System

SoC FPGA devices are available for many commercial operating systems in addition to open source Linux. Below are the partner links for commercial operating systems.

|

Operating system (OS) |

company name |

| Abassi | Code Time Technologies |

| Bare-Metal/Hardware Libraries (in Intel® SoC EDS) | Intel® |

| Carrier Grade Edition 7 (CGE7) | MontaVista |

| DEOS | DDC-I |

| eCosPro | eCos Centric |

| eT-Kernel | eSOL Co., Ltd. |

| FreeRTOS | FreeRTOS.org |

| INTEGRITY RTOS | Green Hills Software (Provided by Japan distributor: Advanced Data Controls) |

| Nucleus | Siemens |

| QNX Neutrino RTOS | QNX |

| RTXC | Quadros Systems Inc. |

| ThreadX | Microsoft |

| µC/OS-II、µC/OS-III | Micrium (Japan distributor: Provided by Techno Logic) |

| µC3 | E-Force Co., Ltd. |

| VxWorks | Wind River |

| Wind River Linux | Wind River |

7-2. Development tools for SoC FPGA

For professional development tools, including JTAG debuggers and instruction trace capabilities, consider:

|

product |

supply vendor |

detail |

| Arm® Development Studio for Intel® SoC FPGA | Intel® | Software development and debugging tools for Intel® SoC FPGA devices based on Arm® Development Studio. Use with FPGA Download Cable II JTAG Debugger Tool or Arm ® DSTREAM Tool for JTAG debug and high-speed instruction trace. |

| Multi | Green Hills | Software development and debugging tools for the Green Hills INTEGRITY real-time operating system. MULTI is connected with Green Hills Probe for JTAG debugging. |

| Poly-Platform, uC/OS-II |

PolyCore Software, Micrium (Japan distributor: Provided by Techno Logic) |

PolyCore Software and Micrium support Cyclone® V SoC in multi-core solutions. This development environment provides a proven message-passing programming model and trusted real-time operating system (RTOS) to facilitate the creation of new multicore designs. |

| Simulink Embedded Coder | MathWorks | Generate C/C++ code for Cyclone® V SoC using Simulink and Embedded Coder from MathWorks. Together with HDL Coder support for Intel® SoC FPGAs, this solution can be used for Intel® SoC FPGA hardware/software workflows spanning simulation, prototyping, verification, and implementation. |

| Sourcery CodeBench | Siemens | GNU toolchain supports dual-core Arm® Cortex®-A9 MPCore processor-based SoC virtual targets. |

| TRACE32 | Lauterbach | Lauterbach TRACE32 is a family of modular processor development tools including debug, trace and instruction set simulators supporting Nios® II processors and dual-core Arm® Cortex®-A9 MPCore processor-based SoCs. |

| Workbench | Wind River | Software development tools for VxWorks running on dual-core Arm® Cortex®-A9 MPCore processors in Cyclone® V SoC and Arria® V SoC. |

7-3. SoC FPGA IP core

intel®SoC FPGAs are supported by a variety of third-party and soft intellectual property (IP) cores. These IP blocks can be instantiated in FPGAs on SoC devices.

Examples of featured SoC soft IP cores are:

|

IP |

supply vendor |

detail |

| graphics rendering | TES Electronic Solutions | 2D, 2.5D, 3D and HD graphics rendering (supports up to EGL 1.3, OpenGL ES 1.1, OpenVG 1.01 API) |

Click here for recommended articles/materials

SoC FPGA related articles and resources

Intel® FPGA Development Flow/FPGA Top Page