When developing a Nios® II processor for Intel® FPGA, the Nios II Software Build Tools for Eclipse (hereafter, Nios II SBT) completes the build,

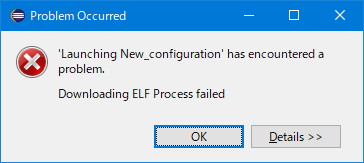

When I try to run Nios II, I get an error and can't run it.

In particular, I often encounter "Downloading ELF process failed" errors.

Here are some of the factors. There is also one point advice at the end of the page.

The factors introduced here are not all, but please check once.

Cause of error

Click each item to see details.

Factor 1. No FPGA configured or running with different versions of Quartus Prime and Nios II SBT

This is the most elementary mistake.

Let's configure the FPGA design with the Nios II we want to run and then use it.

Also, if the FPGA design is compiled with a different version of Quartus Prime than the version of Nios II SBT running Nios II, it may not work properly.

The System ID Peripheral Core ensures that the Configuration Data (.sof) and the Nios II executable (.elf) are inconsistent before running.

[Reference] Points to check when the IDs do not match in the Nios® II System ID Core

Factor 2. In FPGA design, Nios II is clocked incorrectly or reset is stuck

Observe the state of the clocks and resets going into the Nios II using something like the Signal Tap logic analyzer, something that is hard to find with a software approach.

Factor 3. The FPGA design is not timing closed

This is one of the causes of instability, such as being able to download or not, or being disconnected during debugging.

Factor 4. Bad JTAG port connection or design

If the JTAG port is noisy due to bad connections or poor design, the connection may be unstable.

If you are using the Intel FPGA Download Cable II (USB-Blaster II), you can change the TCK frequency. Set to a lower frequency and check again.

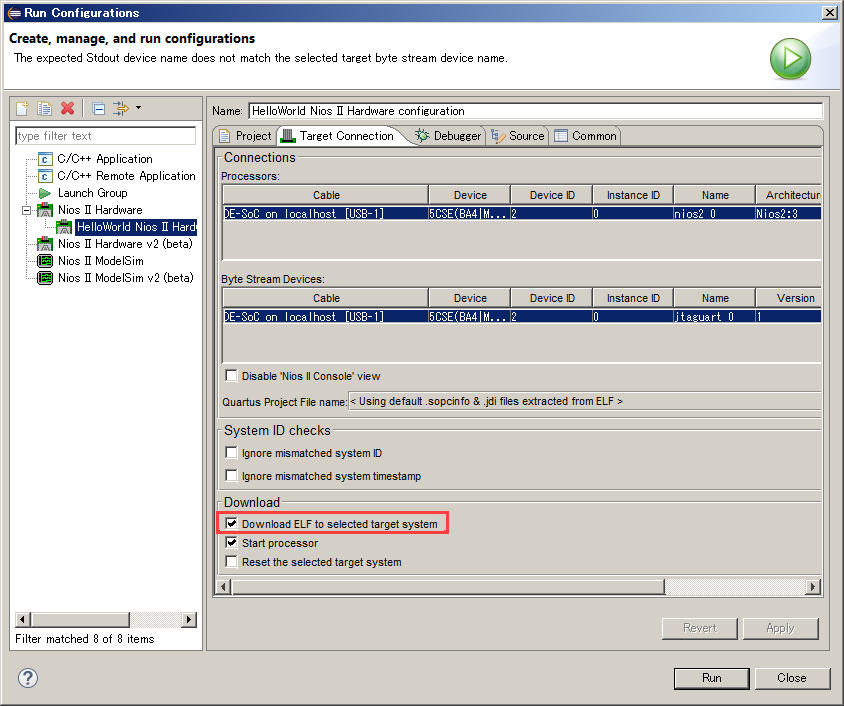

Cause 5. When Reset Vector or Exception Vector is assigned to ROM (when .text is assigned to ROM)

The ROM program cannot be rewritten directly from the Nios II SBT.

If you want to debug an executable program written in ROM

Nios II SBT Run Configuration > Target Connection tab > Download ELF to selected target system option

Please uncheck and execute.

Factor 6. If a module that induces bus lock is installed

This is a common phenomenon that occurs when a user-created module is implemented in Platform Designer, such as accessing an unimplemented address or operating a signal that is not defined by Avalon ®-MM (Avalon ® Memory Mapped Interface). Doing so may lock up the Interconnect Bus in Platform Designer.

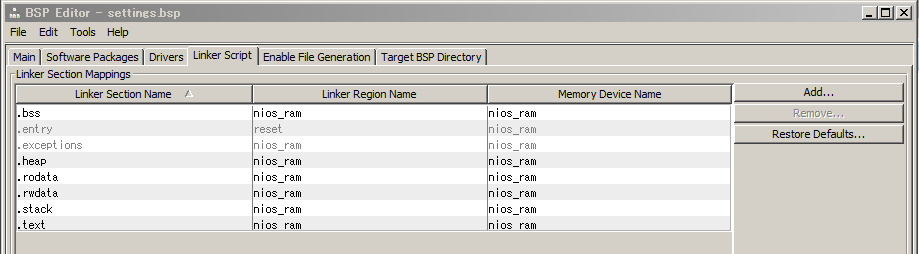

Cause 7. The download target memory is flash memory

Only RAM can be downloaded directly from the Nios II SBT.

In the case of flash, it is necessary to write the software in advance using another tool. (Except when running after expanding to RAM)

This means that if you allocate a .text area to ROM, the Nios II SBT will attempt to download software to ROM, which will "get an error".

To check the memory allocation, open the bsp-editor and look at the Linker Script tab.

You can check the memory allocated to each section as shown below. (In the example below, everything is located in on-chip memory named nios_ram.)

As mentioned above, even if Reset Vector is ROM, if .text is placed in RAM area, downloading from Nios ® II SBT is possible.

Please refer to the following content for the Debug method in the XIP configuration that places .text in ROM.

One point advice

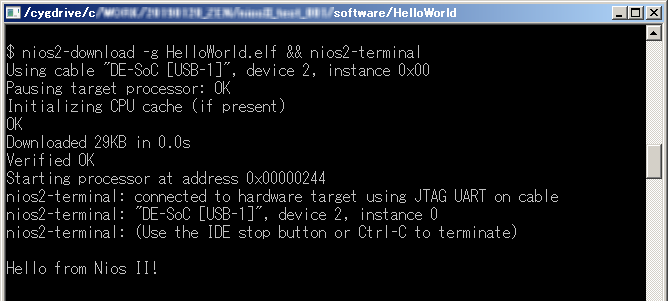

If you get the above error, try running the software from the command line (Nios II Command Shell).

The logs from that time may help identify the cause.

Launch the Nios II Command Shell and download the software using the following commands.

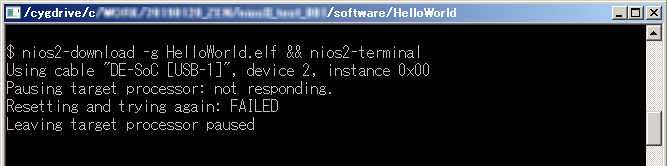

$ nios2-download -g xxx.elfTo also print the output from JTAG_UART to the command line

$ nios2-download -g xxx.elf && nios2-terminalRun as

The log at this time is as follows.

■ Normal

■ Abnormal

In the above case, you can see that Nios II is not accepting requests from Nios II SBT.

As mentioned earlier, this is often due to reset connections and polarity.

You may be able to guess the problem in this way, so please try it.

Click here for recommended articles/materials

Nios® II Processor on Intel® FPGA