hello.

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

In the past, I introduced Logic Lock, which specifies the placement of lower-level entities in Quartus® Prime, but this time, as an advanced version, how to apply the placement-specified lower-level entities with Logic Lock in another project. Introducing

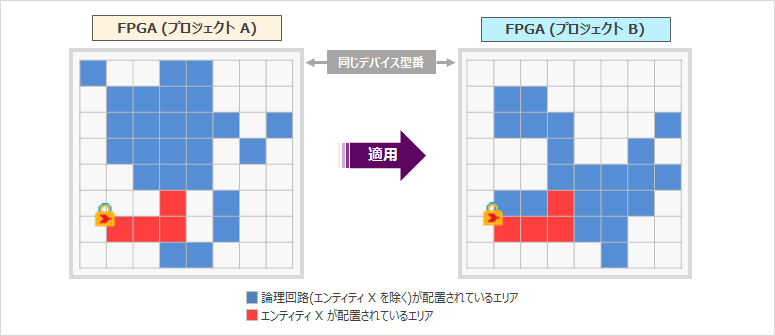

The figure below is an image diagram when Entity X placed in FPGA by Logic Lock in Project A is implemented in FPGA in Project B.

In this way, if you assign placement constraints to entity X with Logic Lock during the development stage of project A, the placement status can be inherited as is in project B as well.

By this method, Entity X can keep timing fixed even in Project B, so it can be expected to reduce the man-hours for timing closure of the entire design in Project B.

Overview

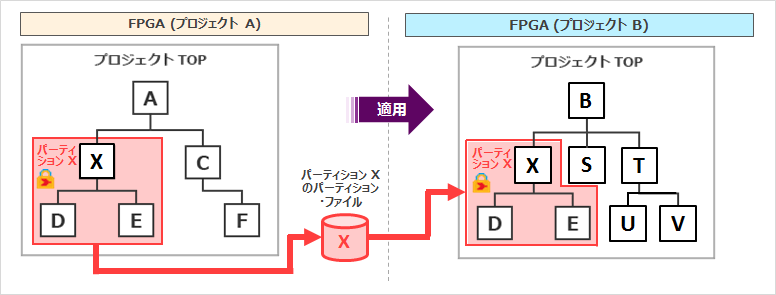

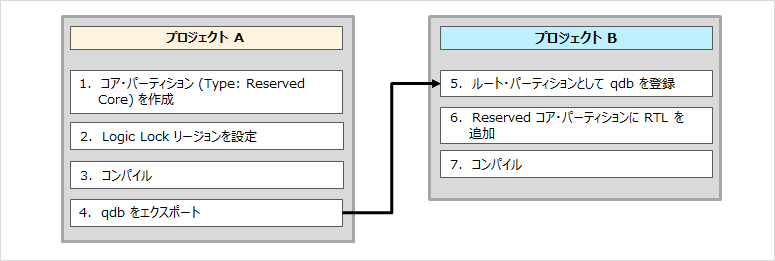

The figure below is an image of the work to apply the lower entity with Logic Lock set to another project.

In order to inherit the compilation result of entity X with placement constraints between projects, in addition to the Logic Lock setting for entity X at the time of project A, create a logical framework called “partition”. Then run a compile on project A and place it as per the constraints.

In order to inherit this compilation result to project B, a special file "partition file" containing the logic circuit information of entity X and the compilation result is generated.

The partition file has different formats depending on the Quartus Prime edition you use.

| Quartus Prime Standard Edition | Quartus Prime Exported Partition File (.qxp) |

| Quartus Prime Pro Edition | Quartus Prime Partition Database File (.qdb) |

In project B, compile using the partition files generated in project A instead of the HDL source files.

In other words, if you want to adopt this flow, at the time of project A, you need to create a partition for the appropriate entity and compile it.

Related information: Try using incremental compilation

Work flow of each edition

The work flow differs depending on the Quartus Prime edition.

Quartus Prime Standard Edition

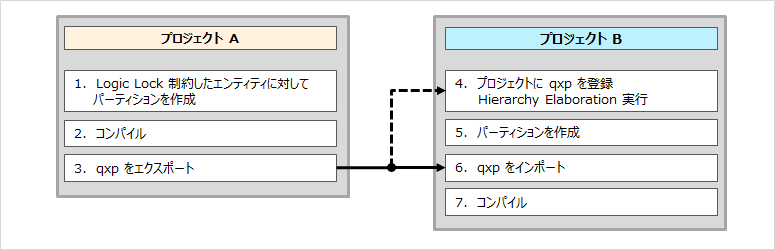

The figure below is a flowchart of the work in the Standard Edition. Export the partition file qxp for the subentity partition and reuse it in another project.

Now, I will introduce this flow in the Quartus Prime menu.

How to Apply Placement Constrained Subordinate Entities to Another Project (Standard Edition)

Quartus Prime Pro Edition

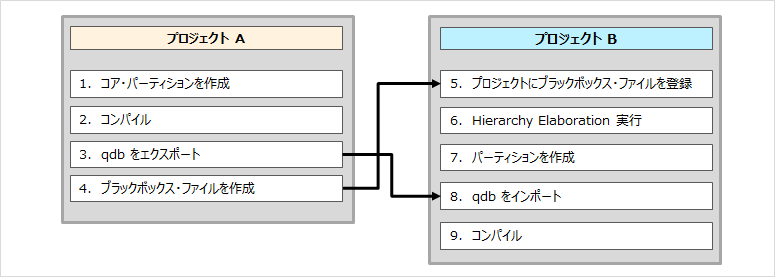

The Pro Edition has the following two patterns for partition specifications. Both export the partition database file qdb for the partition and reuse it in another project.

| core partition | Only core resources (LUTs, registers, M20K memory blocks, and DSPs) can be included. |

| root partition | The root partition contains peripheral resources (including I/O, HSSIO, PCIe, PLL), and associated core resources, but leave the core partition open for further development. |

The figure below is a flow chart of the work in the Pro Edition.

Now, I will introduce this flow in the Quartus Prime menu.

How to apply placement constraint subordinate entities to another project (Pro Edition)

Click here for recommended articles/materials

How to Specify the Placement of Subordinate Entities in a Design (Logic Lock)

How to recompile only part of the FPGA design

Quartus® Prime has a way to reduce compilation time

Try to use incremental compilation

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Do MAX 10 devices support incremental compilation?

Is it possible to generate a .qxp (Quartus II Exported Partition) file with Quarus II Web Edition?