This Quartus® Getting Started Guide series is for users who are new to the Intel® Quartus® Prime / Quartus® II development software.

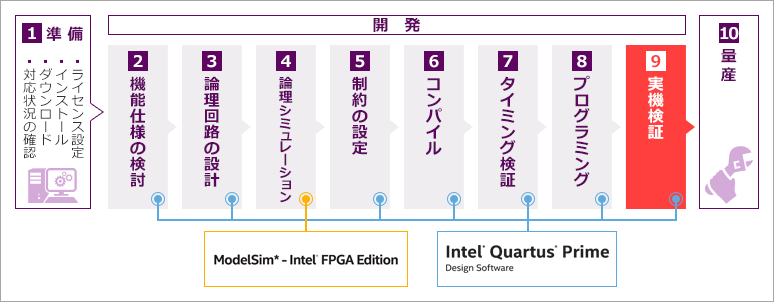

See here for FPGA/CPLD development flow.

explanation

This document will serve as a reference in the "9. Actual device verification" phase of FPGA / CPLD development.

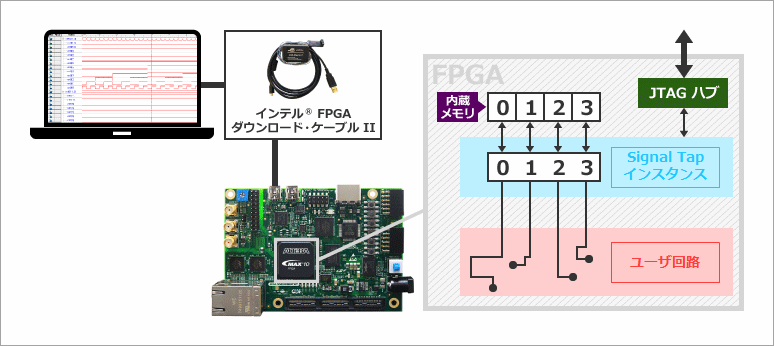

Quartus® Prime comes standard with the Signal Tap logic analyzer, an on-chip debug environment that allows you to verify the behavior of internal signals without taking advantage of unused I/O pins while running your design on the FPGA. increase.

This document describes how to use the Signal Tap logic analyzer.

Although current FPGAs are large and high performance, limitations on packages and unused I/O pins make debugging difficult.

is getting harder. To mitigate that situation, Intel has decided to run the design on an FPGA while still

On-chip debug environment Signal Tap logic to verify internal signal behavior without using I/O pins

We provide a signal analyzer (hereafter, Signal Tap).

The Signal Tap feature is a standard on-chip debugging tool in Quartus® Prime that allows you to view the internal signals of the FPGA running on your board without using external measurement equipment such as logic analyzers or oscilloscopes. can be captured and displayed.

Incorporate the free IP core for Signal Tap into your design, place and route it inside the device, program the data and then run it on the board. The captured data is stored once in the device's internal memory area, then transferred from the JTAG pins on the board to Quartus® Prime via the communication cable, where it is displayed as waveforms on the computer screen. Signal Tap can also run in a board environment with multiple FPGA devices in a single JTAG chain.

Note that this SignalTap has the same function as SignalTap II that was installed in Quartus® Prime v17.0 and earlier versions.

vinegar. The name has been changed from v17.1. (See [TIPS])

Document

"Quartus Prime Getting Started Guide - Using the Signal Tap Logic Analyzer (Document for tool version: Ver.17.1)

Click here for recommended articles/materials

Try FPGA on-chip debugging "Signal Tap"

Quartus® Prime related articles and resources

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Click here for recommended seminars/workshops

Quartus® Prime Introductory Trial Course <Free>

Custom microcomputer design trial ~Experience embedded design using MAX® 10 FPGA! ~ <free>