こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

以前 「マクニカ製 HDMI IP を使って FPGA で4K動画を映してみた」 でもご紹介した Mpression HDMI 2.0 IP を、Arria® 10 FPGA に実装してみました。

インテル® FPGA で HDMI を実現するには

HDMI を実現できるスペックを持つ FPGA を採用する必要があります。

つまり、トランシーバー PHY 内蔵の FPGA に限定されます。マクニカ製の HDMI IP は、HDMI 1.4b および HDMI 2.0 に対応していて、採用するバージョンに対応した FPGA ファミリを選定します。

※ HDMI 規格の各バージョンの基本性能とインテル® FPGA のトランシーバー PHY の最大スペックは、「マクニカ製 HDMI IP を使って FPGA で4K動画を映してみた」 の Table 1 および Table 2 をご覧ください。

Arria® 10 には以下の3タイプあります。それぞれトランシーバーの性能が異なりますが、最大伝送速度が 18 Gbps (1レーンあたり最大 6 Gbps)である HDMI 2.0 のフルスペックを実現するには、十分なデバイスです。

| Arria® 10 シリーズ | Arria® 10 GT | Arria® 10 GX | Arria® 10 SX |

| トランシーバーの 最大スペック(bps/ch) |

25.78 G | 17.4 G | 17.4 G |

前回は Cyclone® V GX(トランシーバーの最大スペックは 3.125 Gbps/ch)だったのでフレームレートを下げて 4K に対応させましたが、今回の Arria® 10 は 4K/60p で動画を映します。

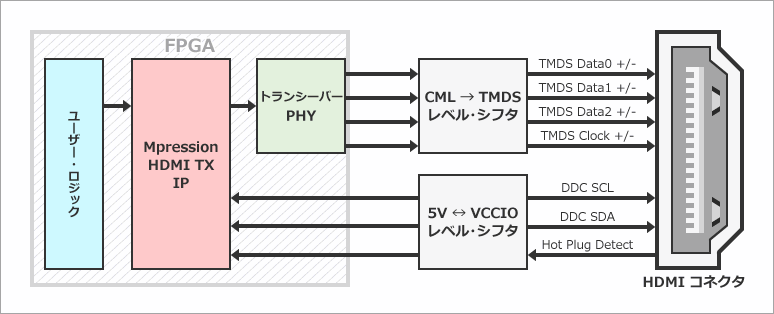

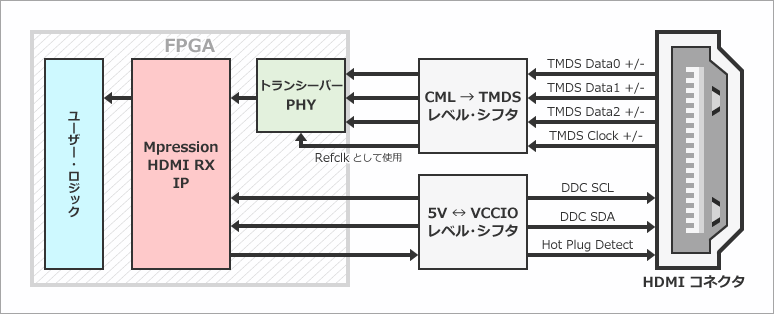

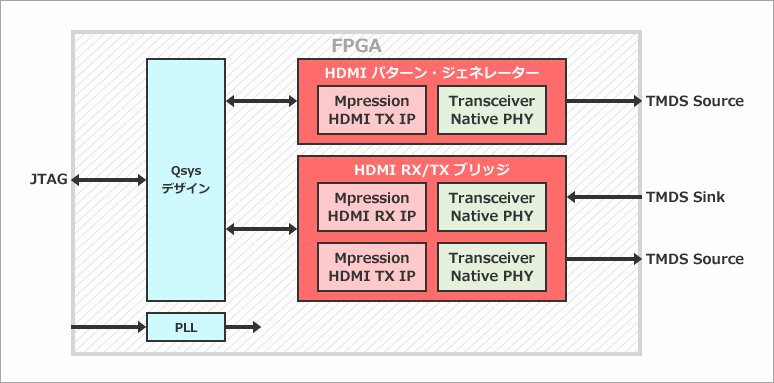

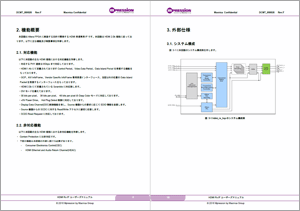

下のイメージ図は、HDMI を実現するための構成です。

HDMI TX IP / HDMI RX IP

HDMI のプロトコルを管理します。

IP のライブラリは、暗号化されたファイルで提供されます。

IP をインスタンスする際の補助ファイル(Quartus® Prime の IP Catalog で言うところの *_inst.v/*_inst.vhd、*.cmp)は現在提供していないそうなので、ユーザーズ・マニュアルを見てポート接続部分を記述するか、あるいは HDMI IP と一緒に提供されるサンプル・プロジェクトのデザインを参考にコピペ&編集してインスタンスを接続します。

トランシーバー PHY

FPGA に内蔵されたトランシーバー部分を採用するには、Quartus® Prime に標準搭載された無償で使用できる IP コア Transceiver Native PHY を使用します。

IP Catalog を使ってターゲット・デバイス向けの Transceiver Native PHY を選択し、ユーザーの仕様に合わせてレシーバ(RX)、トランスミッタ(TX)を個別あるいは共通にライブラリを作ります。

希望する帯域幅に合わせてパラメータを設定し完成させます。仮に FPGA 開発が初めてのユーザーさんでも、リファレンス・デザインが Quartus® Prime のプロジェクトごと提供されるので、そのデザインを参考に作れば簡単に構成できます。

CML/TMDS レベル・シフタ

TX/RX いずれも、データおよびクロック信号に対して CML – TDMS のレベル変換が必要です。HDMI のメインリンクは TMDS(Transition Minimized Differential Signaling)方式で、インテル® FPGA のトランシーバー PHY がサポートする I/O 規格 では直に接続することができないため、CML(PCML) - TMDSに変換し FPGA へ接続させます。

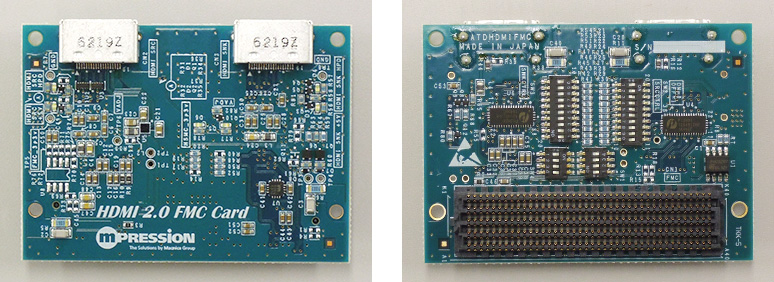

今回の評価実験では、その変換部分に マクニカ製の HDMI ドータ―カード(※)を採用しました。

※ 販売中です。お問い合わせはこちら

5V/VCCIO レベル・シフタ

DDC ラインおよび Hot Plug Detect は 5V I/O で、近年の FPGA は 5V I/O を搭載していないために必要です。

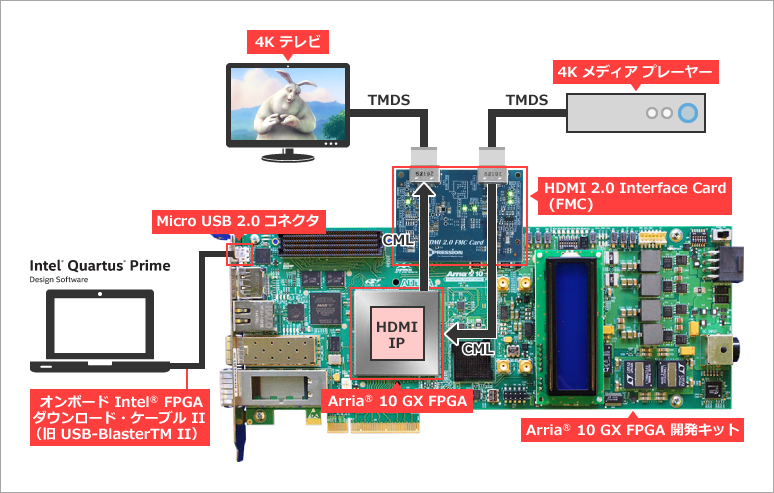

評価ボード環境

今回使用した評価ボード環境は、以下のとおりです。

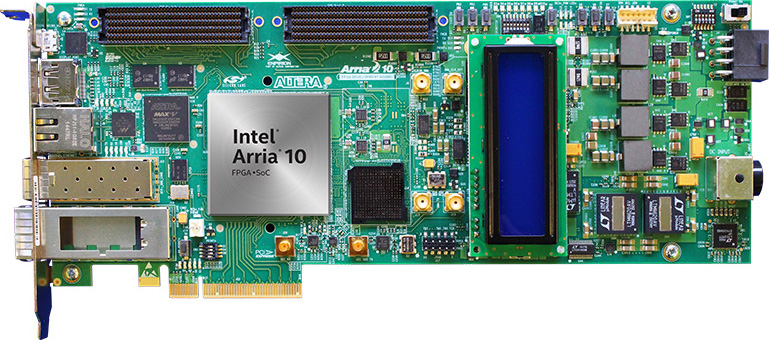

- Intel® Arria® 10 GX FPGA 開発キット(Macnica-Mouserにてご購入/ Intel® PSG サイト)

- Mpression HDMI 2.0 ドータ―カード

評価用リファレンス・デザイン

HDMI 2.0 IP は、 IP ライブラリだけでなく、IP 評価用の Quartus® Prime のリファレンス・デザインも提供しているので、デザインの評価や再構築、新規プロジェクトのテンプレートとしても活用でき、設計者の負担を軽減してくれます。

さらに、Arria® 10 向けのリファレンス・デザインにのみ、デバッグ用のパターン・ジェネレーター回路も構成されているため、簡単に動作評価を行うことができます。

Arria® 10 向け HDMI 2.0 IP のリファレンス・デザインは2種類の評価が可能です。

リファレンス・デザイン [評価 1]

4K メディアプレーヤーの出力映像を HDMI 2.0 IP で受信し、そのまま HDMI 2.0 IP から送信して 4K テレビに映像を表示

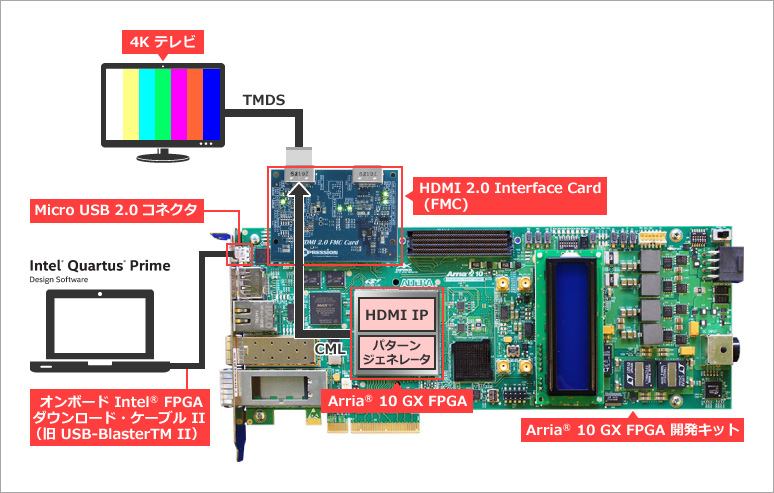

リファレンス・デザイン [評価 2]

Arria® 10 GX 内部に構成したパターン・ジェネレーターから生成した様々なテスト・パターンを送信用 HDMI 2.0 IP から 4K テレビに出力

リファレンス・デザインのブロック構成は下図のとおりです。

PLL は、その Transceiver Native PHY をドライブするためのクロック周波数の生成用として構成しています。このマクロも Quartus® Prime に標準搭載されているので無償で使用できます。こちらも IP Catalog を使って作り、Transceiver Native PHY 同様に、提供されるサンプル・プロジェクトを参考にして自分の仕様に応じた設定値にします。

もし解像度を 4K ⇔ フル HD ⇔ HDというように動的に切り替えられるようにする場合には、さらに トランシーバーおよび PLL のリコンフィギュレーション用デザイン を作成します。こちらも Transceiver Native PHY 同様に、提供されるサンプル・プロジェクトを参考に、仕様に適用させます。

実機で動作させてみた

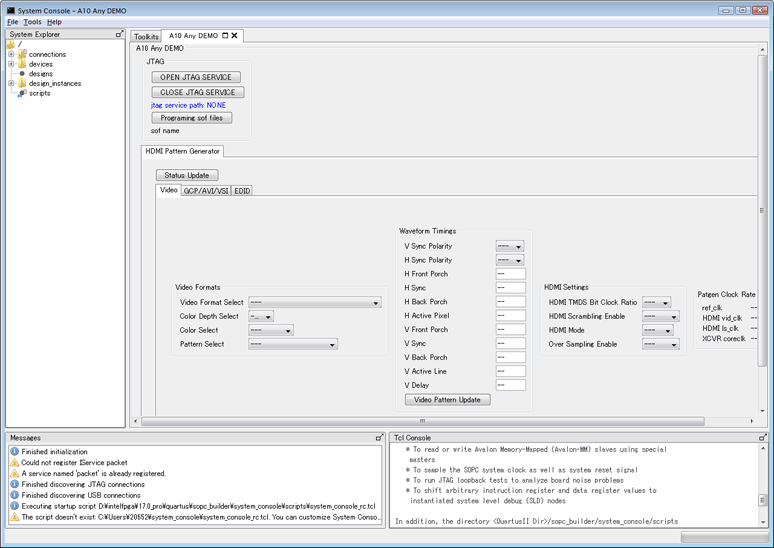

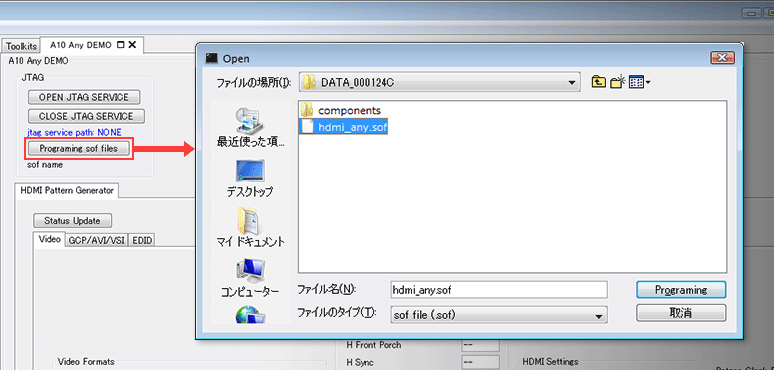

リファレンス・デザインの実機評価を行うときには、Quartus® Prime に標準搭載された System Console(システム・コンソール)を使用します。

SOF ファイルのダウンロードや、表示させるテスト・パターンの解像度/タイプなどの制御も System Console 上から行います。

この System Console で行う評価スタイルは Arria® 10 限定に構築された環境で、 今回の目玉です!!

システム・コンソールとは?

システム・コンソールとは、FPGA でデザインを実動作させながらデバッグを迅速かつ効率的に行う上で役立つ、極めて柔軟性に優れたシステム・レベルのデバッグ・ツールです。

システム・コンソールでは、システム・レベルのリード/ライト・トランザクションを Qsys システムに送信できるため、問題の切り分け/特定に役立ちます。また、システム・クロックの確認やリセット状態のモニタを素早く簡単に行うこともできるため、ボード立ち上げの際にも役立ちます。さらに、ボタン、ダイヤル、グラフなどの GUI 機能を使用して独自のカスタム検証ツールやデモ・ツールを開発することにより、さまざまなシステム・レベル・トランザクションを表現して、データ処理をモニタリングすることも可能です。

詳細は、メーカーのホームページをご覧ください。

デモ [評価1]

まずは、4K メディアプレーヤーの出力映像を Arria® 10 GX の HDMI 2.0 RX/TX IP を経由して、そのまま 4K テレビに映像を表示させるデモ [評価1] です。

System Console を操作し、SOF ファイルを Arria® 10 GX にダウンロードします。

4K メディアプレーヤーから出力させる映像の解像度を選択し再生すると、4K テレビに指定した解像度の映像がきれいに映し出されました!

実は、4K メディアプレーヤーの解像度を指定(変更)するたびにその情報が System Console に送信され、System Console が自動的に Arria® 10 GX 内のトランシーバーのパラメータを変更してくれるため、ユーザーは何も手を煩わすことなく、4K テレビに指定した解像度の映像が映し出すことができる仕組みになっているんです。

デモ [評価2]

続いて、Arria® 10 GX 内部に構成したパターン・ジェネレーターから生成したカラーバー・パターンを HDMI 2.0 RX IP から 4K テレビに表示させるデモ [評価2] です。

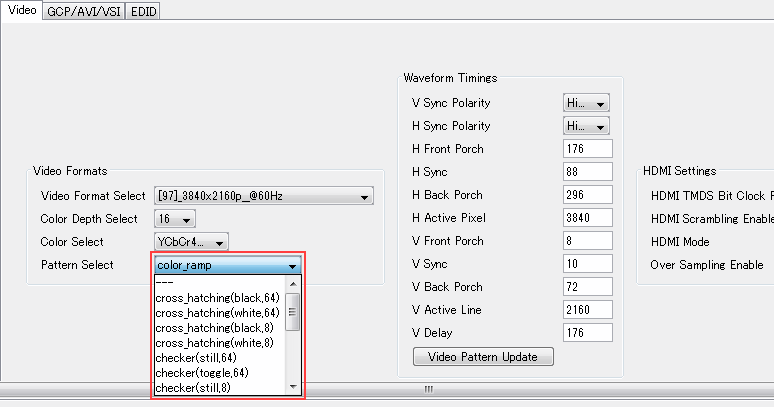

パターン・ジェネレーターを GUI で制御してみます。

HDMI Pattern Generator タブ内の Video タブには、テレビに表示させる映像パターン情報がすでに組み込まれていて、Video Formats セクションにおいて、Video Format Select で 解像度(42パターン)、Color Depth Select で色深度(4パターン)、Color Select で色空間(4パターン)、Pattern Select で映像パターン(16パターン)が指定できます。

ユーザーはここを選択するだけで OK!

Waveform Timings セクションの V Sync、H Sync などの極性や期間、HDMI Settings セクションの Sink 機器にセットする内容などは、Video Formats セクションの選択項目に応じて自動で設定されます。なんて便利!

本当に簡単に表示させるテスト・パターンを変えることができ、素早い検証が行えます。

最後に

いかがでしたか?

この IP を使うと、本当に簡単に Arria® 10 GX で HDMI 2.0 のインターフェースが構築できました!

HDMI 2.0 IP は、TX と RX 別々に購入することができますので、用途に応じて使用することができます。是非ご検討ください。

Mpression の HDMI IP は、以下のアイテムが用意されています。

- HDMI IP ライブラリ(暗号化 VerilogHDL ファイル)

- HDMI IP シミュレーション・ファイル(ライブラリ、テストベンチ)

- リファレンス・デザイン用 Quartus® Prime プロジェクト一式・ユーザーズ・マニュアル(※)

- リファレンス・マニュアル(※)

- シミュレーション・マニュアル(※)

※ マニュアルはもちろん日本語です。

この他、採用を検討しているユーザーには評価用ラインセンスの発行もしてくれます。

また、IP 開発部隊は日本(新横浜)にいますので技術サポートもクイック・レスポンス!スタッフは日本語で対応します。だから購入後も “安心サポート!” ユーザーのリクエストにも可能な限り対応してくれるそうです。

マクニカ製 HDMI 2.0 IP または HDMI ドータカードに興味がある方は、下記へご連絡ください。