With the shift of logic circuits from TTL to CMOS, the noise margin on the amplitude axis has become significantly wider in terms of performance. On the other hand, the clock frequency has improved by two to three orders of magnitude compared to the TTL era.

First TTL era

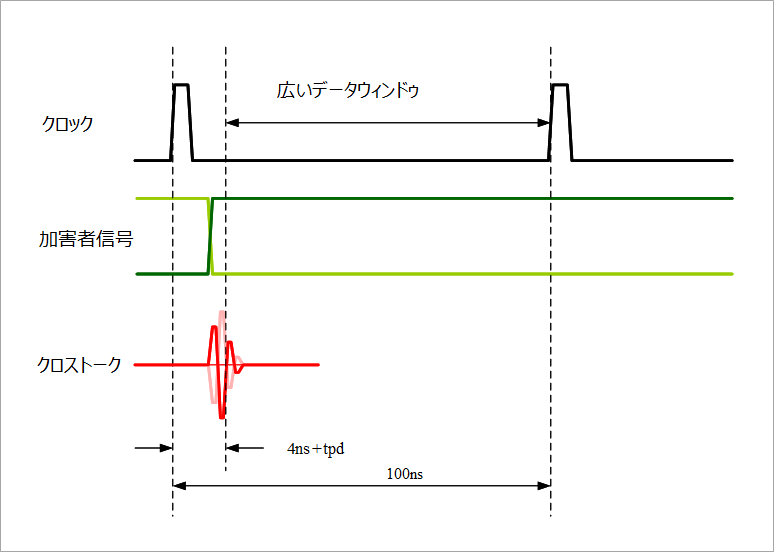

For example, consider crosstalk in the case of TTL with a clock frequency of 10MHz as shown in Figure 1. Suppose the design is bad and you have to clear the second peak (valley). If the wiring length is 15 cm, the time required for one-way signal is τ=1 ns. The crosstalk pulse width in Figure 1 is 2τ = 2ns. So the window is 4ns narrower than 100ns.

100ns - 4ns, ie 96ns, considering setup/hold times of a few ns each, so we have a wide data window. (Actually, it is necessary to consider the delay time of the perpetrator's signal.) Even if the clock is 5 times this 50MHz, the period is 20ns, so there is still a considerable margin.

However, TTL is not slow and CMOS is fast. (footnote)

fast CMOS

If the clock frequency is 500MHz, the cycle is 2ns. Even if the wiring length is 4 cm (τ = 0.25 ns), considering the second valley (peak) as above, 4τ = 1 ns, so there is no such margin. Even if it is unavoidable, wait 2τ=0.5ns until the first peak (trough) subsides. 0.5ns is hard for a period of 2ns, so it is necessary to avoid exceeding the noise margin with crosstalk noise.

On the other hand, the understanding of signal integrity has deepened, and designs have been made to reduce reflections and crosstalk. Therefore, glitches on the amplitude axis are much less likely.

From noise margin to timing margin

While malfunctions on the amplitude are decreasing, interest in the time axis has increased from the amplitude axis due to the speedup.

As explained in "Concept of Noise Margin", the noise margin has increased from 0.4V in the TTL era to 1.0V, and further increased to about 1.5V when differential single input is used. Also, although not explicitly stated in the datasheet, the uncertainty in the threshold voltage eats into the timing margin.

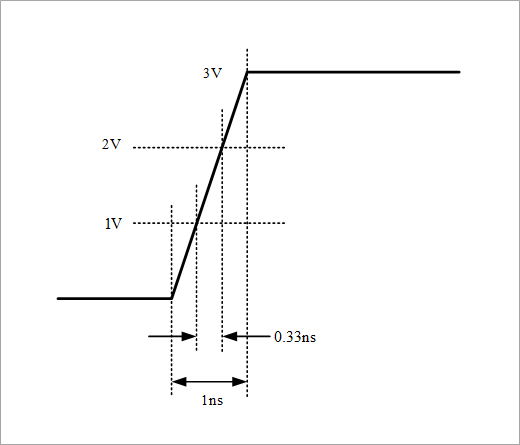

For example, as shown in Figure 2, when the signal rise time is 1 ns (0-100%) and the threshold voltage uncertainty is 1 V/2 V, the timing uncertainty is 0.33 ns. If the clock frequency is 500MHz, 0.33ns is 16% of the 2ns period and cannot be ignored. Using a differential single input avoids this time uncertainty.

Noise superimposition when signal changes

Noise reduction design and elements that avoid threshold ambiguity have greatly improved the noise problem. Noise is not only superimposed on logic signals of "0" and "1" as in the past, but new problems have become apparent when noise is superimposed during transitions.

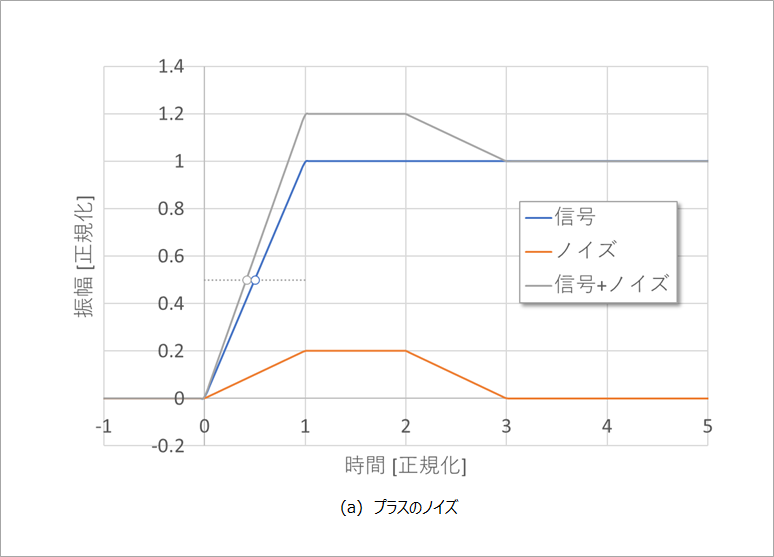

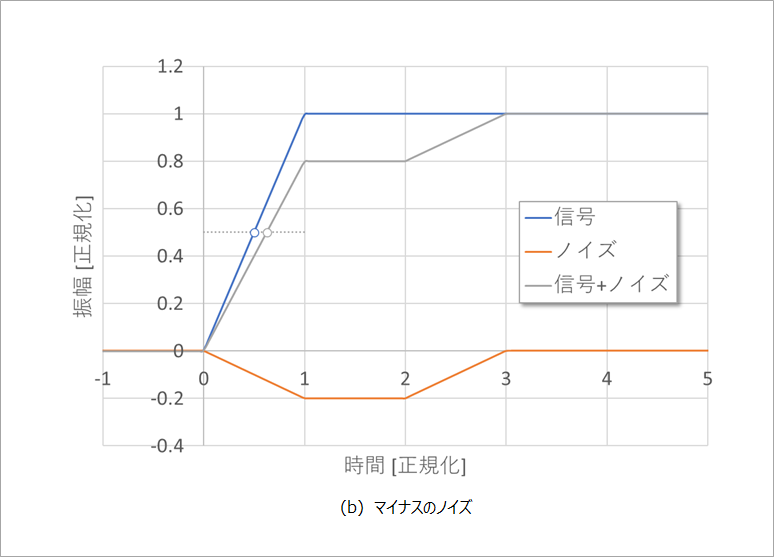

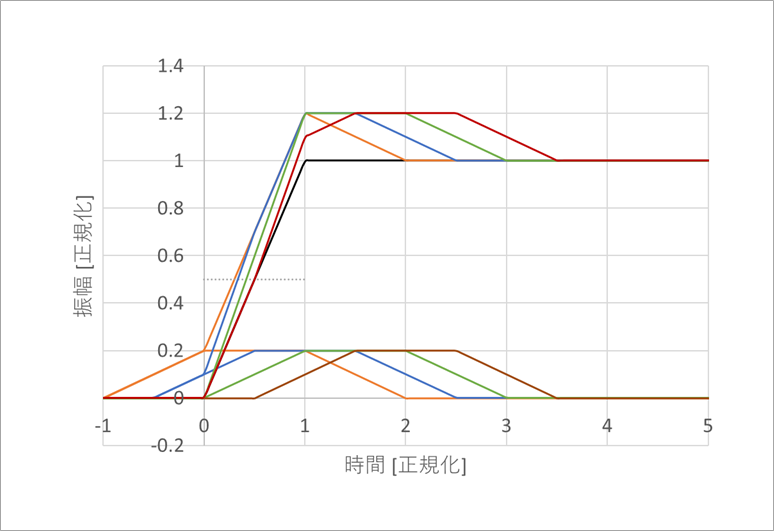

As shown in Figure 3, the threshold shifts when noise is superimposed near the rising edge of the signal. Positive noise speeds up the rising edge, and negative noise slows it down. Figure 3 normalizes the rise time and amplitude to 1 each. If you think of time in ns and amplitude in volts, you can get a concrete image.

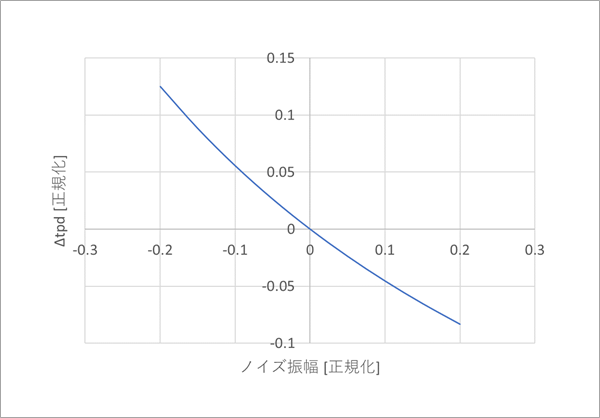

Figure 4 shows the change in delay time when the noise amplitude is varied under the conditions of Figure 3. roughly proportional to the amplitude.

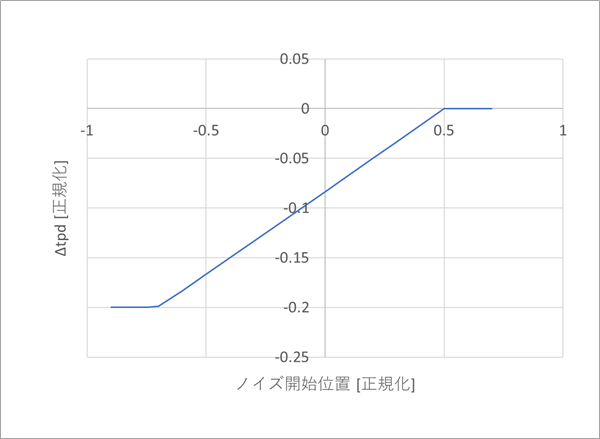

Figure 5 shows changes in waveform depending on the noise start position, and Figure 6 shows changes in the noise generation position and delay time. Naturally, when the noise peak position coincides with the rising edge of the waveform, the change in delay time is maximized. Figures 5 and 6 are for positive noise, but the same is true for negative noise.

If the timing of the victim signal and the position of the noise can be identified, the timing design will be performed based on that timing.

This concept must be considered as jitter in the case of gigabit transmission. Even minute noise appears as timing jitter, which narrows the eye. It is no exaggeration to say that the design margin has shifted from the amplitude axis to the time axis.

(footnote)

The CMOS in the heyday of TTL was the 4000 series. TTL gate delay time is 10ns, CMOS is 100ns or more, and CMOS was used for limited applications such as low power consumption and wide supply voltage.

After that, the 74S and 74AS series appeared one after another, followed by the 74LS series for low power, and many series for a wide range of applications. Since then, CMOS has evolved from metal gates to silicon gates (realization of self-aligned gates), realizing high speed and high integration, and I think it has taken the leading role from TTL.

What is Yuzo Usui's Specialist Column?

It is a series of columns that start from the basics, include themes that you can't hear anymore, themes for beginners, and also a slightly advanced level, all will be described in as easy-to-understand terms as possible.

Maybe there are other themes that interest you!