The Altera® HLS Compiler is now available in all editions (Pro/Standard/Lite) of the Quartus® Prime software starting with v17.1. This article provides the most useful information for users who are just starting to use the HLS Compiler.

What is the HLS Compiler?

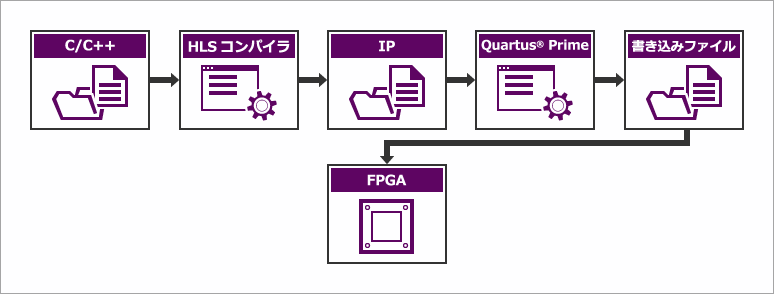

The HLS Compiler is a High Level Synthesis (HLS) tool optimized for Altera® FPGAs. Using this tool, you can create circuits (designs) from software programming languages such as C and C++ for implementation on Altera® FPGAs.

Designs that previously required hardware knowledge can now be created by software designers, allowing system optimization by offloading filter processing written in C or C++ and software processing that was too heavy for the CPU to Altera® FPGA circuits.

HLS Compiler Documentation

Visit this page to view the documentation provided by Altera®.

HLS Compiler introduction page

(English version (Click here)

*For documents, please click on the "Related Materials" tab (or "Documents" for the English page).

The following materials are available:

- Product Summary

- Image Processing White Paper

- Getting started guide

- User guide

- Reference manual

- Best practice guide

- Quick reference guide

- White Paper: "Optimizing QRD Decomposition"

We've introduced several documents, but you may be wondering in what order to read them. Here we'll introduce the order in which to read them to help you understand the overall flow of learning how to use the HLS Compiler.

1. Product overview

This is a product overview of the HLS Compiler, giving you a high-level overview of the tool.

First, you need to know how to set up the environment required to use the HLS Compiler. You can also learn about the Example Design in advance, which will serve as a reference when using the HLS Compiler in the future.

For information on how to set up an HLS compiler environment, please see this article.

Setting up the HLS compiler environment (Windows®)

2. User Guide

Once you have set up the tool, you can learn the practical flow: the user guide will guide you through the steps of creating a component using the HLS Compiler, synthesis, verification, and simulation.

This guide explains the steps for synthesizing, verifying, and simulating IP designed for Altera® FPGA products. It also includes information on creating a simulation test bench during synthesis, as well as basic commands for verification and simulation. It also includes instructions for using the generated IP in Quartus® Prime, limitations of the HLS compiler, and an overview of reports.

3. Best Practice Guide

Learn how to optimize performance with the HLS Compiler, including loop optimization, optimal memory architecture configuration, and optimizing component data types and conversions to improve performance and reduce logic area.

If you create a component and it doesn't perform as expected, try the optimizations described in the documentation. This documentation provides examples of how to use the tool to identify bottlenecks and how to optimize them.

By reading the documents in the order listed above, you can learn about the features of the HLS Compiler. There are also other documents that contain useful information. Although not listed in the flow above, please refer to them as needed.

Other resources are listed below:

Other materials

Image Processing White Paper

Using image processing as an example, you can learn about the HLS Compiler design flow. This guide explains the algorithm, its C++ implementation, and how to use the HLS Compiler to implement it in hardware, verify it, and optimize it.

This book uses concrete examples to explain the implementation flow when using the HLS compiler, making it the perfect resource for understanding the process from specification consideration to implementation and optimization.

Getting started guide

This book contains information necessary for setting up the environment, such as the tools and license settings required to use the HLS compiler, and an introduction to example designs. It is a very useful resource for users who are just starting to use the tool.

It also includes troubleshooting information for licenses, which can be useful if you are having trouble setting up your license.

Reference manual

Refer to this when you have trouble specifying command options or component attributes.

This document contains information necessary for actual design, such as HLS compiler command options, component and interface attribute descriptions, etc. Please refer to it when editing source code or executing commands for the HLS compiler after component attributes and interfaces have been determined.

The Appendix also provides a quick reference list of command line arguments and component attributes, which can also be used to search for arguments, commands, etc.

White Paper: "Optimizing QRD Decomposition"

We can use eigenvalue decomposition as an example to understand optimization methods.

This guide provides an example of how to improve the performance of QR decomposition code using the optimization methods introduced in the Best Practices Guide. You can use this example to understand specific optimization methods when using the HLS Compiler.

Experience the HLS Compiler

By following the materials in the order presented on this page, you can quickly begin evaluating the HLS Compiler.

I hope that using the HLS compiler will reduce labor costs and serve as the first step toward software designers taking on hardware design.

We have prepared articles and materials such as how to set up the environment and simple tutorials, so please try using the HLS Compiler.

Click here for recommended articles/materials

Setting up the HLS compiler environment (Windows®)

HLS Simple Tutorial

High Level Synthesis related articles and materials

Altera® FPGA Development Flow / FPGA Top Page