Overview

High frequency switches using wide band gap semiconductors contribute to efficient power conversion. One example is a silicon carbide switch, which can be implemented as a SiC MOSFET or a SiC cascode JFET in a cascode configuration.

This article traces the origins of SiC cascode JFETs and their evolution to the latest generation, and compares their performance with other technologies. Over the course of four parts, we explain the differences in physical properties, the approach and features for an ideal switch, reliability, and unique uses in real applications.

Proving the reliability of SiC cascode JFETs

In addition to the high temperature and voltage resistance of wide band gap switches, the advantage of SiC cascode JFETs is that they do not use SiC gate oxide like SiC MOSFETs, which are subject to degradation by high electron beams. Cascode Si-MOSFETs are robust low-voltage types with high threshold voltages and thick gate oxides, and are further protected by built-in Zener clamps. In fact, SiC cascode JFETs are so reliable that they now routinely achieve automotive AEC-Q ratings. The key is their reliability when subjected to unintended stresses such as overvoltages and short circuits. SiC cascode JFETs have a robust avalanche phenomenon that is activated by the destruction of the drain gate of the JFET.

As a result, the current flowing through Rg in Figure 2 (Approach and Features for an Ideal Switch) drops the voltage, turning on the JFET and clamping the overvoltage. Although Si MOSFETs do experience avalanches in this way, they are highly controlled and consume very little power because the avalanche protection diodes are included in the manufacture of each cell. SiC MOSFETs also have avalanche ratings, but GaN HEMT cells do not, so manufacturers must evaluate their parts at low voltages to ensure sufficient margin between operating and breakdown voltages.

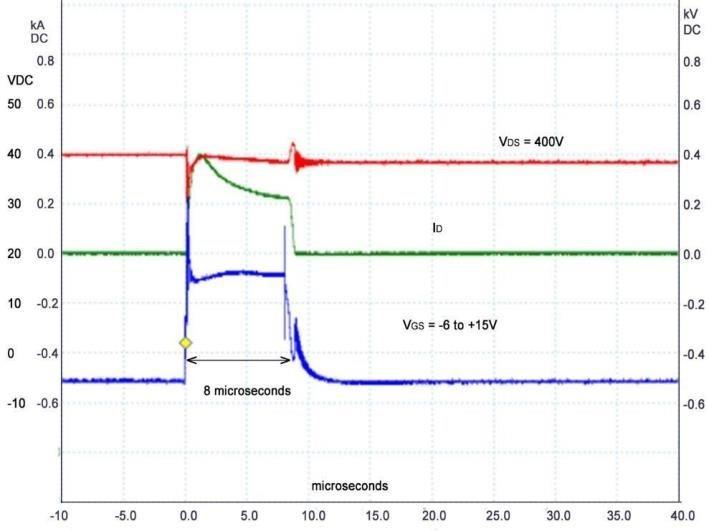

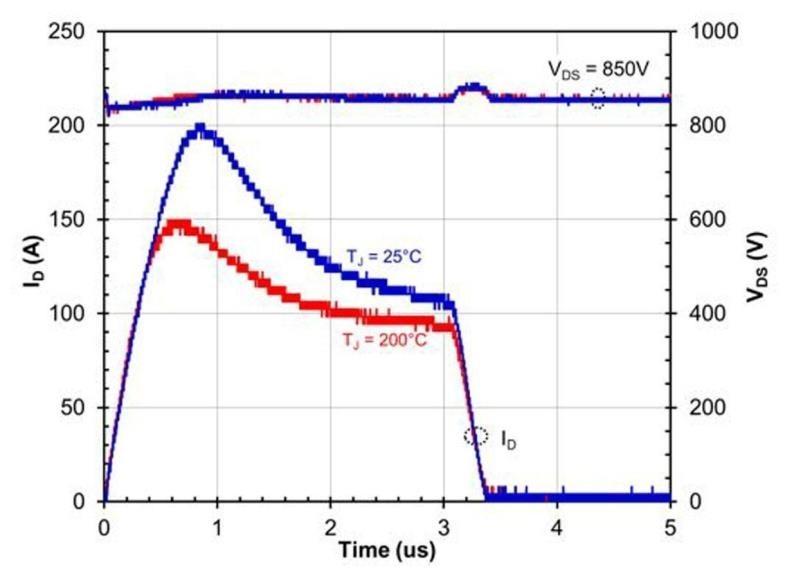

SiC cascode JFETs also have a gentle short-circuit current characteristic. At high currents, the gradient of the voltage drop across the channel causes a natural "pinch-off" effect to limit the current. The short-circuit current is independent of the gate voltage, unlike MOSFETs and IGBTs, and the positive temperature coefficient of the on-resistance of the SiC cascode JFET 's channel also reduces the limiting current and helps distribute the stress to the individual cells within the die. This effect is so stable that SiC cascode JFETs can be used as precise current-limiting devices in linear circuits. Figure 1 shows that a 750V SiC cascode JFET survives an 8μs stress with no degradation. Figure 2 shows the effect of the on-resistance increasing with temperature and the short-circuit current decreasing to a final value that is nearly independent of the initial junction temperature for a 1200V rated SiC cascode JFET.

To maintain reliability, temperature rise and temperature gradients in packaged SiC cascode JFETs must be minimized, and SiC has the advantage of having thermal conductivity three times higher than silicon and GaN. The latest devices also use sintered silver rather than solder for die attachment, improving interface thermal conductivity by six times, reducing junction temperature rise and keeping reliability high.

Inquiry

If you have any questions regarding this article, please contact us below.

On Semiconductor Manufacturer Information Top Page

If you want to go back to ONSEMI maker information top page, please click below.