This Quartus® Guide series is for users of the Intel® Quartus® Prime / Quartus® II development software.

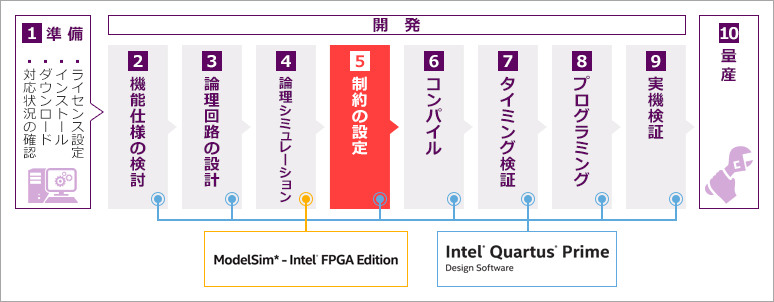

See here for FPGA/CPLD development flow.

explanation

This document can be used as a reference in the "5. Constraint Setting" phase of FPGA/CPLD development.

Introduces how to set commonly used pin options in the Quartus® Prime / Quartus® II development software.

Use the Assignment Editor and Pin Planner in the Quartus ® Prime / Quartus ® II development software to set pin options when you want to assign a specific function to a pin or an internal signal.

Document

Note that the title of this document has been changed from that for v15.1.

"Quartus Prime - How to Set Commonly Used Pin Options ver.15.1" (Document for tool version: Ver 15.1)

"Quartus II Beginner's Guide - How to Set Commonly Used Logic Options ver.14" (Document for tool version: Ver 14.0)

Click here for recommended articles/materials

Quartus® Prime related articles and resources

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Click here for recommended seminars/workshops

Quartus® Prime Introductory Trial Course <Free>

Custom microcomputer design trial ~Experience embedded design using MAX® 10 FPGA! ~ <free>