Introduction

Hello, I'm Topu.

This time is a continuation of the last time (Relationship between Quartus® and board simulation - Guide to IBIS file ①).

Since we completed creating the topology for the simulation and assigning the model in the last time, let's finally start the simulation this time.

Run the simulation

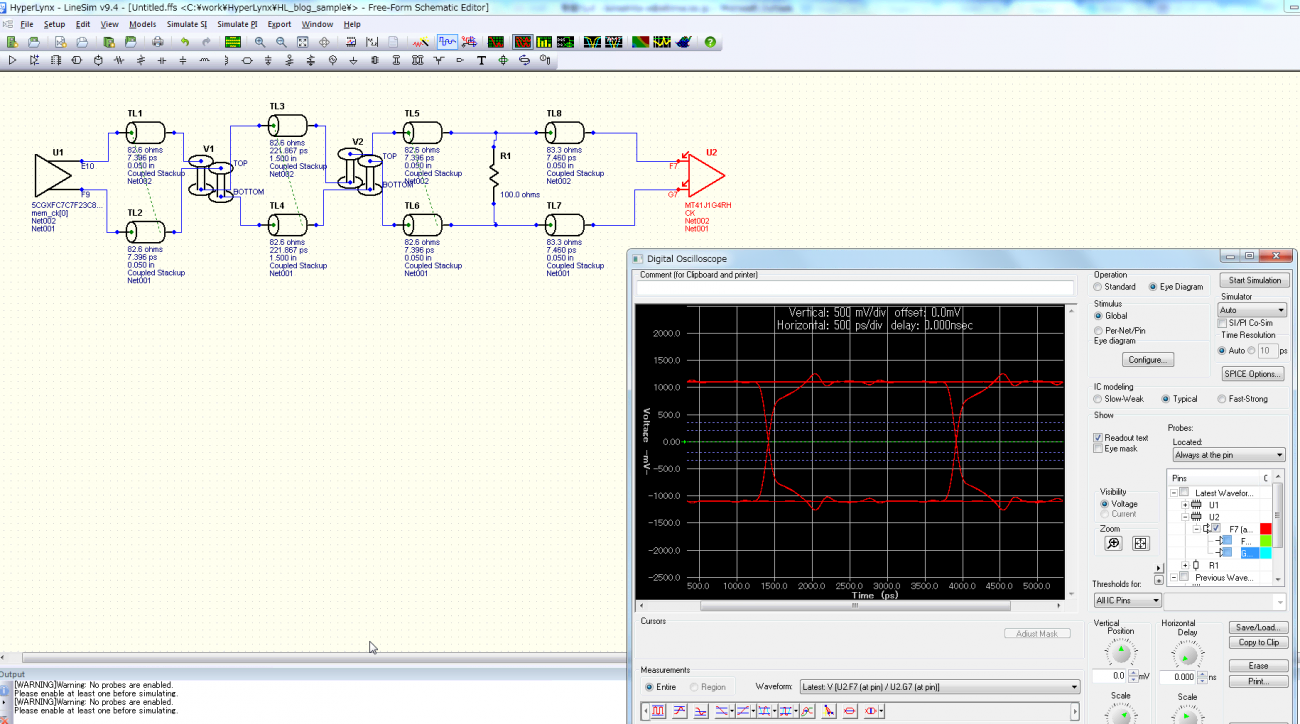

Open the previously created topology in HyperLynx® and launch Run Interactive Simulation and Show Waveforms.

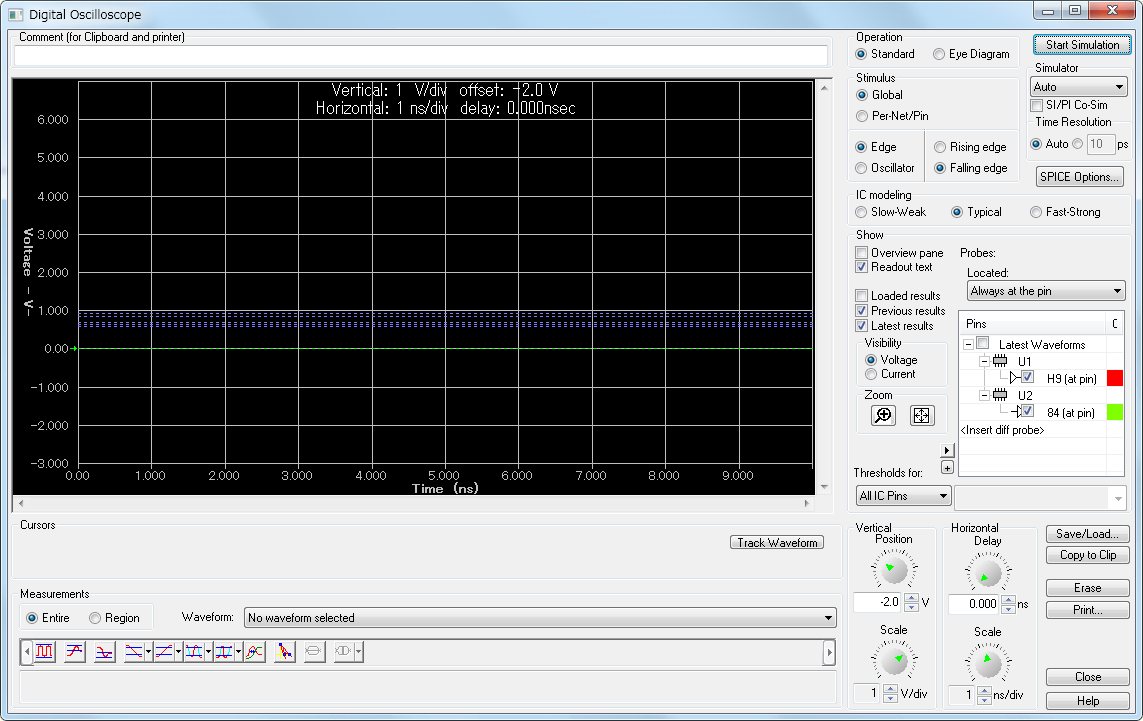

The Digital Oscilloscope window will launch.

The Digital Oscilloscope displays the results of IBIS simulations as waveforms.

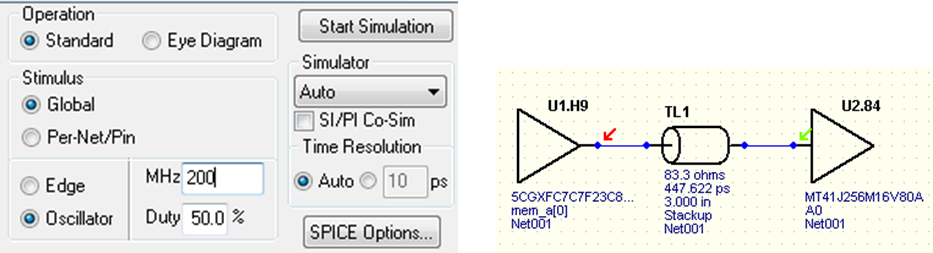

This time, let's simulate the case where the Oscillator outputs a 200MHz signal from the driver. The settings are as follows (Fig. 3).

Click Start Simulation to start the simulation.

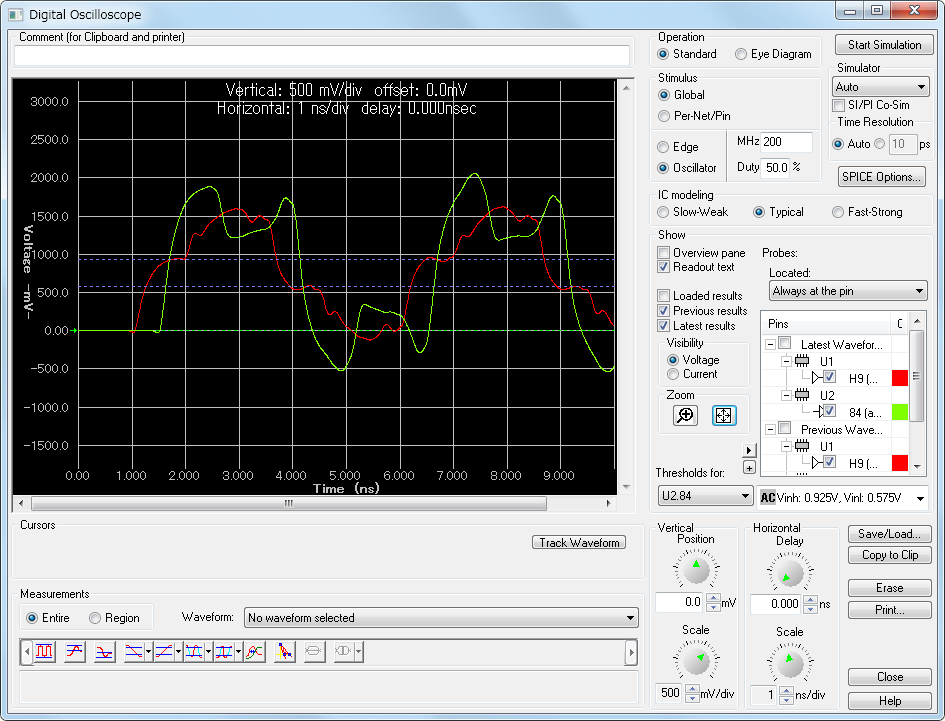

When the simulation is complete, the waveform will appear as shown in Figure 3.

Two waveforms are displayed, red is the driver side waveform and yellow-green is the receiver side waveform.

If you pay attention to the receiver (green) waveform, you can see that the waveform is greatly disturbed.

These are due to the reflection of the signal on the transmission line.

If you want to know the cause of signal distortion, read this article!

This time, we simulated with a very simple topology that just connects a driver and a receiver.

Actually, as shown in Fig. 5, the topology assumed on the board is created on the schematic, and simulation is performed to check the waveform.

By performing a simulation before creating a board in this way, it is possible to confirm the effects of transmission line length, wiring width, etc., and reflect this in the board design, making it possible to establish a design flow with little rework. .

This time, I introduced the method of simulating the IBIS file generated by Quartus.

A variety of verifications are possible with HyperLynx. I will introduce you on another occasion. looking forward to.

MentorGraphics Virtual Lab

Anyone who wants to try HyperLynx.

Do not have. . . It's okay to say! Anyone can try HyperLynx from the site below!

<MentorGraphics HyperLynx SI Virtual Lab>

https://www.mentor.com/pcb/product-eval/hyperlynx-si-virtual-lab

This is a cloud environment that allows customers who have not purchased the product to easily experience MentorGraphics' products.

You can experience the tool with a simple user registration, so please try it!

One last point★

IBIS models are also available on the website.

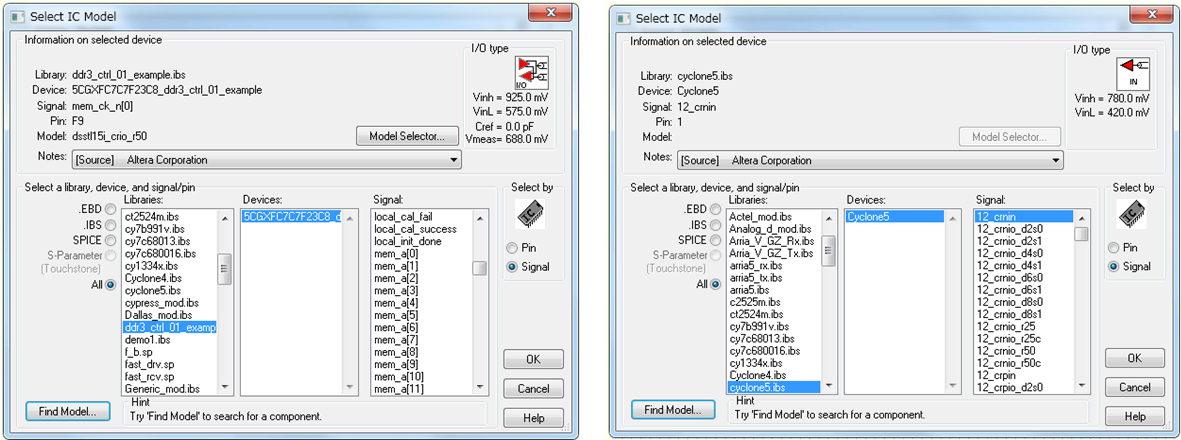

Let's compare the model selection screen of the file obtained from the web and the one generated by Quartus. The one on the left is generated by Quartus, and the one on the right is obtained from the web (Figure 6).

Notice the Signal part.

On the right are similar names such as 12_crnio_d2s0 and 12_crnio_d2s1. This is a model for all possible pin setting combinations for IO in Cyclone® V devices. Cyclone V has over 3000 setting combinations. It is difficult to select the model for the pin setting you use from this list.

On the other hand, the ibis generated from the Quartus project can generate an IBIS file that reflects the settings and names of each pin. This makes model selection easy.

<Also check!> >

The relationship between Quartus and board simulation ~ Guide to IBIS file ① ~ is here.