hello.

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

System Console is a debug tool included in Quartus ® Prime that allows debugging via JTAG while the design is actually running on the FPGA.

You can access registers to peripherals connected to System Console via JTAG, check the JTAG master's clock, and so on.

Also, simple register accesses can be debugged with the System Console without a Nios ® II processor installed.

This time, I will introduce the System Console using a simple sample.

Target environment

| Quartus Prime | Pro Edition / Standard Edition / Lite Edition |

| Target device | All Devices Supported by Quartus Prime Editions |

| communication cable |

Intel FPGA Download Cable II (formerly USB-Blaster II) On-Board Intel FPGA Download Cable II Intel FPGA Download Cable (formerly USB-Blaster) On-Board Intel FPGA Download Cable |

Usage requirements

To use System Console, in your project design,

Must include one of the following peripherals:

・ JTAG to Avalon Master Bridge (JTAG Master)

・ Nios II Processor (with JTAG Debug module)

・USB Debug Master

・ Avalon-ST (Streaming) JTAG Interface

・JTAG UART

・Ethernet components

sample design

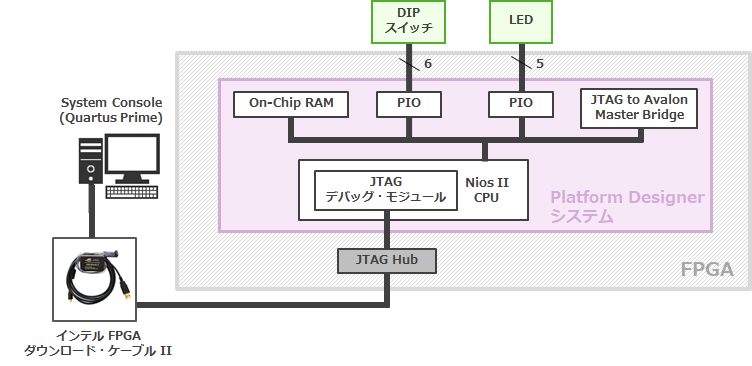

The configuration of the sample design used here is as follows.

This time, using System Console, check the status of the clock signal and reset signal,

Access to DIP switch PIOs, LED PIOs, and on-chip RAM.

This section introduces operations using the Quartus Prime Standard Edition GUI.

System Console debug flow

The work flow for using System Console is as follows.

1. Add and generate IP cores in the Platform Designer system

3. Connect the board and configure the FPGA

1. Add and generate IP cores in the Platform Designer system

Incorporate the IP required to use the System Console into your Platform Designer system.

The components used in this sample design are:

・Nios II Processor (with JTAG Debug module)

・JTAG to Avalon Master Bridge

・On-Chip Memory Intel FPGA IP

・PIO Intel FPGA IP (2)

Note:

Simple register accesses can be debugged with Nios II alone.

In order to use the JTAG Debug service (command) this time, JTAG to Avalon Master Bridge is also connected.

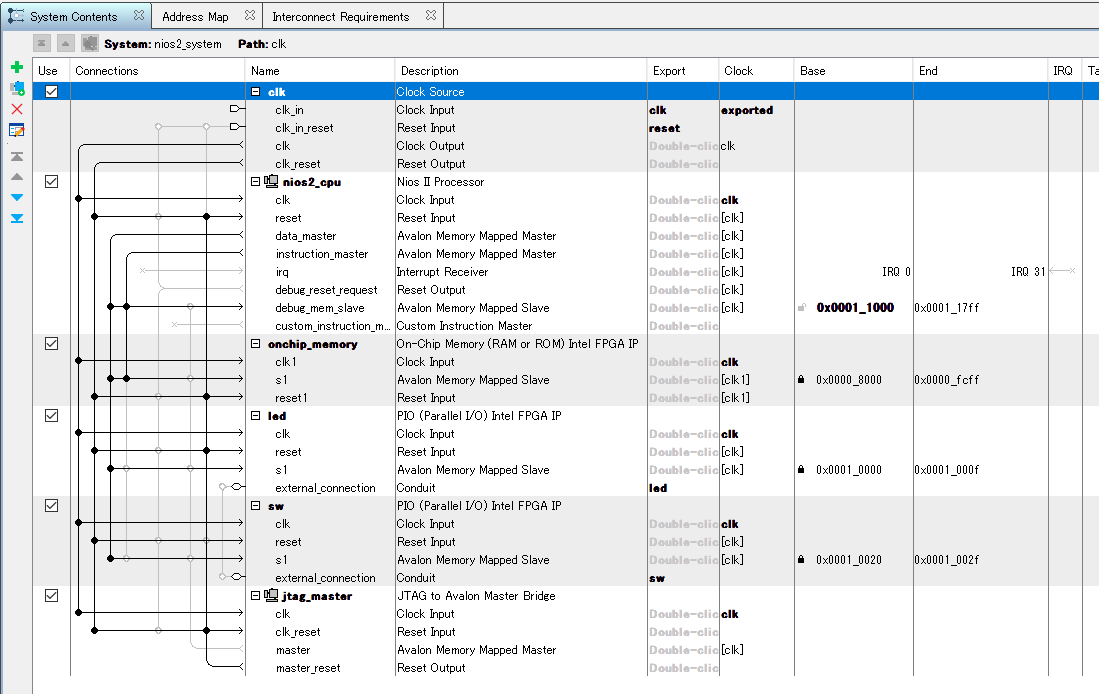

After registering each component in Platform Designer, connect it on the System Contents tab.

Connect the Avalon Memory Mapped Master (hereafter Avalon MM Master) to the Avalon Memory Mapped Slave (hereafter Avalon MM Slave) of the component you want to operate.

Note:

As an example of this sample design, the Master service is executed by Nios II's Avalon MM Master,

The JTAG Debug service is designed to be executed by the Avalon MM Master of the JTAG to Avalon Master Bridge.

The figure below shows the connections in this sample design.

Once completed, save the Platform Designer system and run Generate HDL.

2. Compile the design

Incorporate the created Platform Designer system into the design and register it in the project.

Then run the compile.

3. Connect the board and configure the FPGA

① Connect the board and the download cable, and turn on the power to the board.

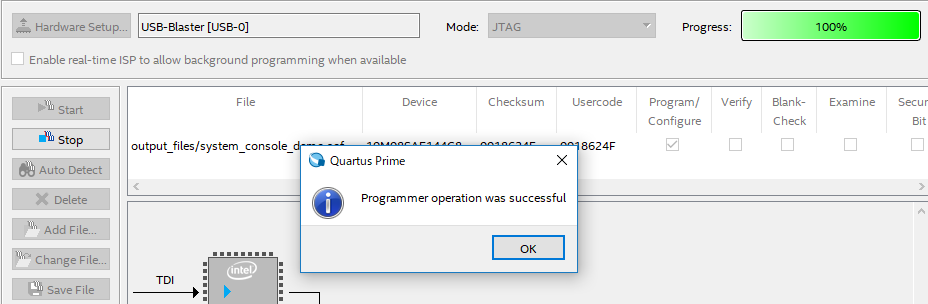

(2) Start Quartus Prime Programmer and select Hardware Setup and sof file to download.

Make various settings.

③ Click the Start button to complete the configuration.

④ Close Programmer.

In addition, FPGA configuration (.sof download) is not done here,

It can also be executed with the device command device_download_sof from the System Console.

See "4. Start System Console" for details.

4. Start System Console

(1) Start System Console.

There are three ways to start up, so please select one according to your development situation.

A) Tools menu > System Debugging Tools > System Console in Quartus Prime

B) Tools menu > System Console in Platform Designer

C) Launch the Nios II Command Shell and enter the system-console.exe command

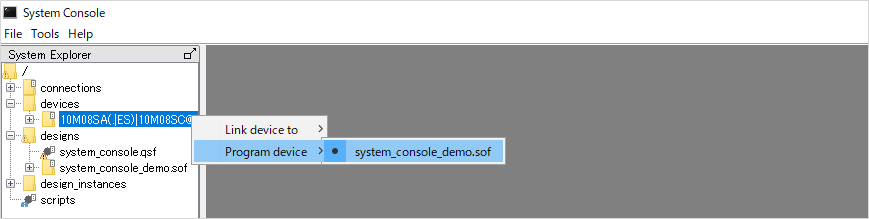

(2) Click File menu > Load Design in System Console and select the downloaded (to be downloaded) .sof.

<If you have already downloaded the .sof, skip to the next step.> >

③ For the connected FPGA under the devices folder in the System Explorer pane,

Right click > Program device > click "sof file".

Alternatively, you can configure the FPGA by entering the following commands in the Tcl Console pane.

% get_service_paths device % set dpath [lindex [get_service_paths device] 0] % device_download_sof $dpath "sof ファイルのパス"5. Specify the service path and identify the service

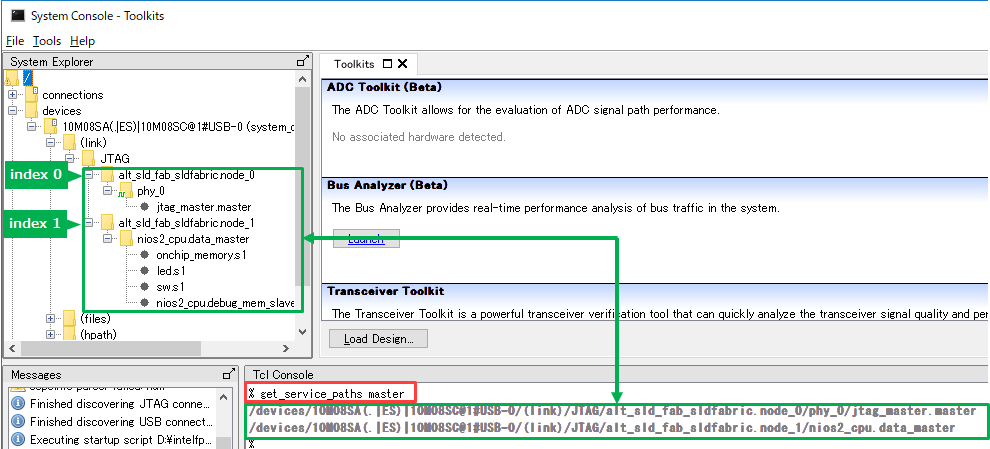

① In the Tcl Console pane, specify the path with the get_service_paths command to identify the service.

You can check the list of service types with the get_service_types command.

For example, in this sample design,

Use the master service to "access DIP switch PIOs, LED PIOs, and on-chip RAM".

Get the master service path by typing:

% get_service_paths masterThe sample design shows two Avalon MM Masters.

In addition to the log of the above command, you can also check it under the devices folder > FPGA part number > (link) folder > JTAG folder in the System Explorer pane.

② In the sample design, each memory-mapped slave is read and written via the Nios II Avalon MM Master.

Create a variable pointing to the Nios II (Avalon MM Master) component by typing:

* mpath is a variable. lindex is 1.

% set mpath [lindex [get_service_paths master] 1]6. Start the service

The claim_service command initiates a connection to the specified service.

% claim_service master $mpath ""To facilitate further debugging work, create a variable in the service started with the command below.

% set master_path [claim_service master $mpath ""]Note : When using the above command, it is not necessary because claim_service master $mpath “” is used at the same time.

7. Execute debug operation

Validate the attached device using the command:

Below are some example commands for this sample.

● When checking the clock and reset signal / when issuing a reset signal

Use the jtag_debug service.

In the sample design, it is accessed through the Avalon MM Master of the JTAG to Avalon Master Bridge, so it looks like this:

* jdpath is a variable. lindex is 0.

% set jdpath [lindex [get_service_paths jtag_debug] 0] % jtag_debug_sample_clock $jdpath % jtag_debug_sample_reset $jdpath % jtag_debug_reset_system $jdpath・jtag_debug_sample_clock : Returns the value of the clock signal (multiple sampling is required for toggle confirmation)

・jtag_debug_sample_reset : Returns the value of the reset signal

・jtag_debug_reset_system : Issue reset to all components connected to Avalon to JTAG Master component

● To check the ON/OFF status of the DIP switch

% master_read_8 $master_path 0x10020 1・master_read_8 : Read the value of the specified address

・0x10020 : PIO address for DIP switch

・1 : Read size

● Control LED ON/OFF

% master_write_8 $master_path 0x10000 0x1F % master_write_8 $master_path 0x10000 0x0・master_write_8 : Write to the specified address

・0x10000 : Address of PIO for LED

・0x1F, 0X0: Value to write

● Read and write to on-chip RAM

% master_read_32 $master_path 0x8000 32・master_read_32 : Read the value of the specified address

・0x80000 : On-chip RAM address

・32 : Size to read

% master_write_32 $master_path 0x8000 {0 1 2 3 4 5 6 7 8 9 10}・master_write_32 : Write to the value of the specified address

・0x80000 : On-chip RAM address

・{0 1 2 3 4 5 6 7 8 9 10} : Value to write

For other commands and services, see the document below.

| Quartus Prime | Reference document |

|

Standard Edition Lite Edition |

Analyzing and Debugging Designs with System Console From the Intel Quartus Prime Standard Edition User Guide: Debug Tools |

| Pro Edition | From "Intel Quartus Prime Pro Edition User Guide: Debug Tools" |

8. End service

Close the connection to the service started in operation 6 with the close_service command.

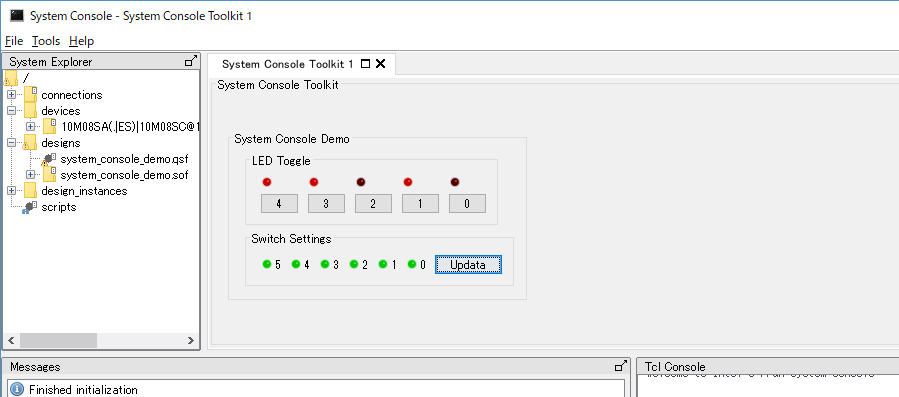

% close_service master $master_path[Advanced] Run with Toolkit API

Toolkit API services allow you to visualize debug data and display graphical widgets such as buttons, text Box, bar graphs and dials by scripting commands that you would otherwise type into the System Console's Tcl Console pane. .

Next time, I will introduce the Toolkit API.

Summary

System Console allows you to send system-level read/write transactions to the Platform Designer system,

Helps isolate and identify problems.

It is also useful during board bring-up as it is possible to quickly and easily check the system clock and monitor the reset state.

System Console に関するコンテンツ (メーカー Web サイト)

Web page

* When viewing the linked video in Video Demonstrations,

Requires JavaScript enabled and the latest version of Adobe Flash Player.

Online training (free)

YouTube