みなさん、こんにちは、もつです。

今、研修で FPGA を用いた時計を製作しています。

デザインは Verilog HDL と VHDL の両方で作成しました。

まずはじめに、 Verilog HDL で完成させました。

I thought that VHDL would be difficult, but my senior told me, "If it's written in Verilog, just change it!"

I was relieved that I could do it right away!

しかし実際にやってみると、案の定エラーだらけ…

「そんな簡単にはいかないよな」と思い、一つずつ見直していくことに。

よく見てみると、勘違いしていたところが多々ありました。

So, this time, I will introduce some of the grammatical differences between Verilog HDL and VHDL that I misunderstood in my training.

クロックでの立ち上がり処理

In Verilog, when processing is performed at the rising edge of the clock,

always @ (posedge clk)

と書いていましたが、

VHDL では、

process ( clk )begin

if ( clk ‘event and clk = ’1’ ) then

と書かないといけない!

I've been writing only Verilog HDL for a while, so I've completely forgotten about it, and I was wondering if I should just write it on the sensitivity list. (lol)

複数行書いても、begin...end がいらない!?

例えば、Verilog HDL では、ステートメント記述が2行以上になる時は、begin...end が必要 でしたが、

VHDL では書き方が異なります。

process 文の後には begin...end をつけますが、if 文の後ろには then が必要で

その if ステートメントが終了する場合には、end if が必要 です!

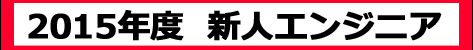

コメントアウトの仕方が違う!?

In Verilog HDL,the comment out was "//" (double slash), and "/* ... */" for multiple lines.

Commenting out in VHDL 1993 is "--" (double hyphen), and when commenting out multiple lines, all lines must be preceded by a double hyphen.

I thought it was a little troublesome, but there was an easy way! !

By clicking the Toggle Comment button (red circle below) in the Quartus II text editor tool bar, you can comment out all the selected lines at once.

Moreover, I was told by a senior later

In VHDL-2008, it seems that /* … */ in Verilog HDL can now be commented out.

論理演算子に記号が使えない!?

論理演算子を記述するとき、

Verilog HDL is written with "symbols", but VHDL cannot use symbols as shown in the table below.

|

論理演算子 |

Verilog HDL |

VHDL |

|

論理否定 |

! |

not |

|

論理積 |

&& |

and |

|

論理和 |

|| |

or |

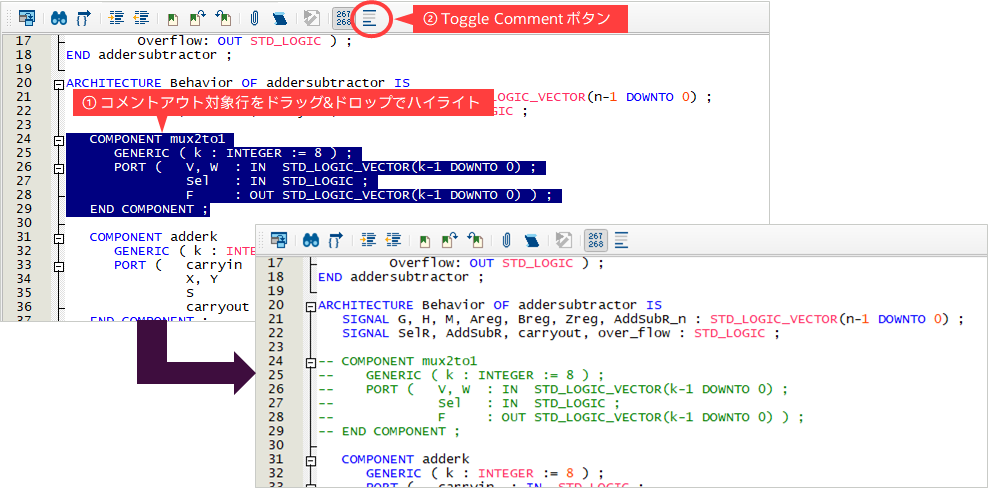

If 文中での数字の表現について

Verilog HDL では、例えば、4 ビットの 9 を 10 進数で表現するには、4’d9 のように表記していました。

しかし、

I thought, "In VHDL, there was no such way of notation...", so I wrote everything in binary.

ですが、良く調べると、10 進数で書く方法がありました!

VHDL で 2 進数で 4 ビットの 9 を表記する場合は、"1001" と書きますが、

これを 9 とそのまま書けば良いのです!ダブルクオート("")で囲む必要もないです!

ただしこれは、if 文の中の条件判定の場合のみです(下図)。

値の代入の際などに使ってしまうと、integer タイプと認識され、エラーとなるので注意が必要です。

以上が、私が研修で時計を作っている際につまずいた点です。

6 月の研修で、Verilog HDL も VHDL も少し学んだのですが、いざイチからやってみると、勘違いしているところ、忘れていたところが多々ありました。

Please use it as a reference.