This time, using the PDN tool provided by Intel, we will introduce a method for calculating an appropriate capacity guideline.

Intel's PDN tool (2.0 is the latest as of September 15, 2015) is a tool that calculates the appropriate capacity, number, and shape of decoupling capacitors when designing a board (PCB) on a board with an FPGA installed. It's a tool to do that.

PDN's software DL and manual are here ↓

Using the capacity calculated by the PDN tool as a guide, optimize the power supply device, and change the capacity as the case may be. By easily calculating the appropriate capacity for both the FPGA and the power supply device, the work efficiency of the board design is greatly improved. can be uploaded to

This time, we will introduce Cyclone V SoC as a base.

Now let's take a look at how to use the PDN tool.

Step 1: Select an FPGA

Select the family and model number and finalize the power supply configuration.

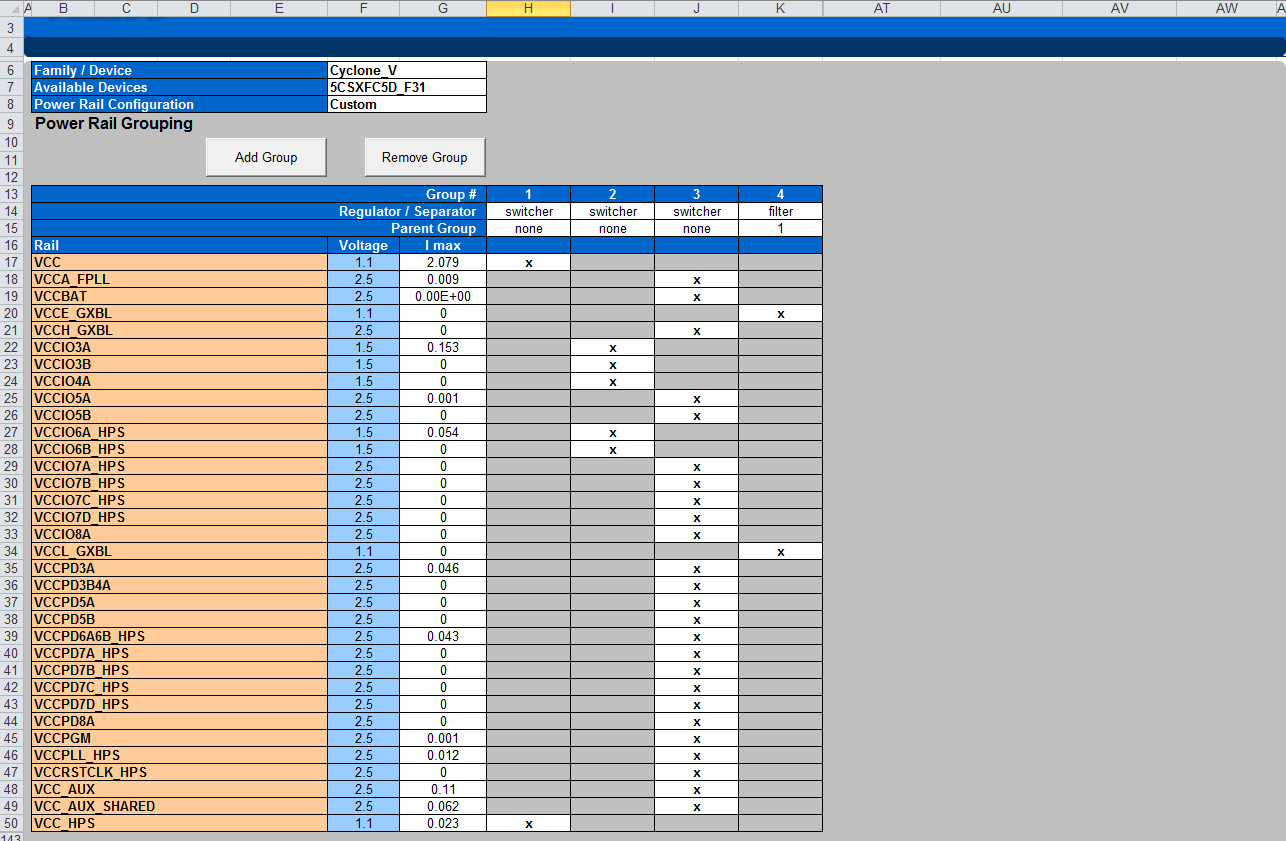

Step 2: Enter the power supply configuration and values calculated by Early Power Estimator (EPE)

Enter the value calculated by EPE, select power supply device or Filter, select X or X/related to create a power supply configuration

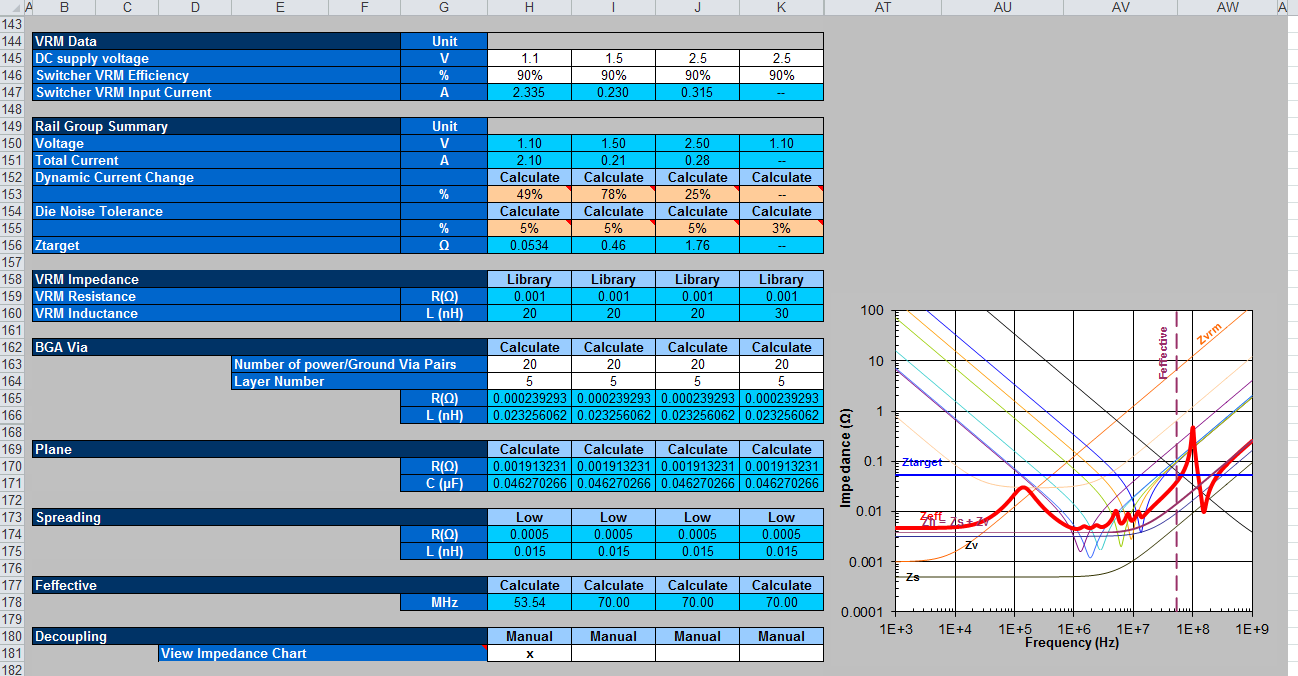

Step 3: Select power device, regulator selection, number of vias, resistor values, number of board layers, etc.

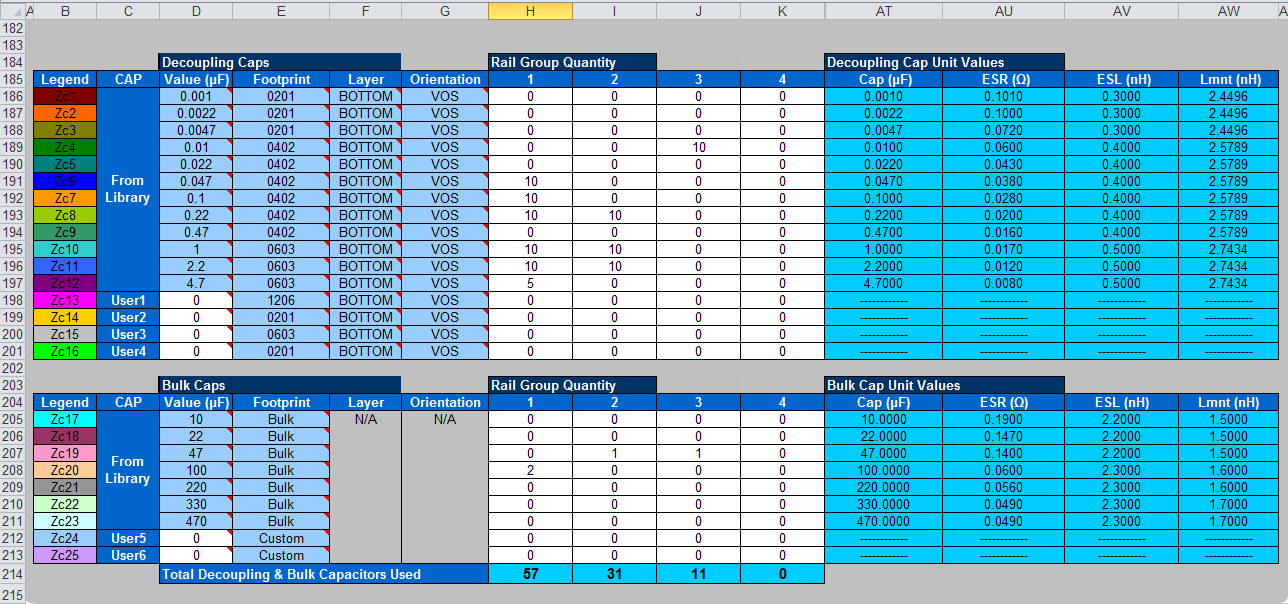

Step 4: Enter the number of capacitors

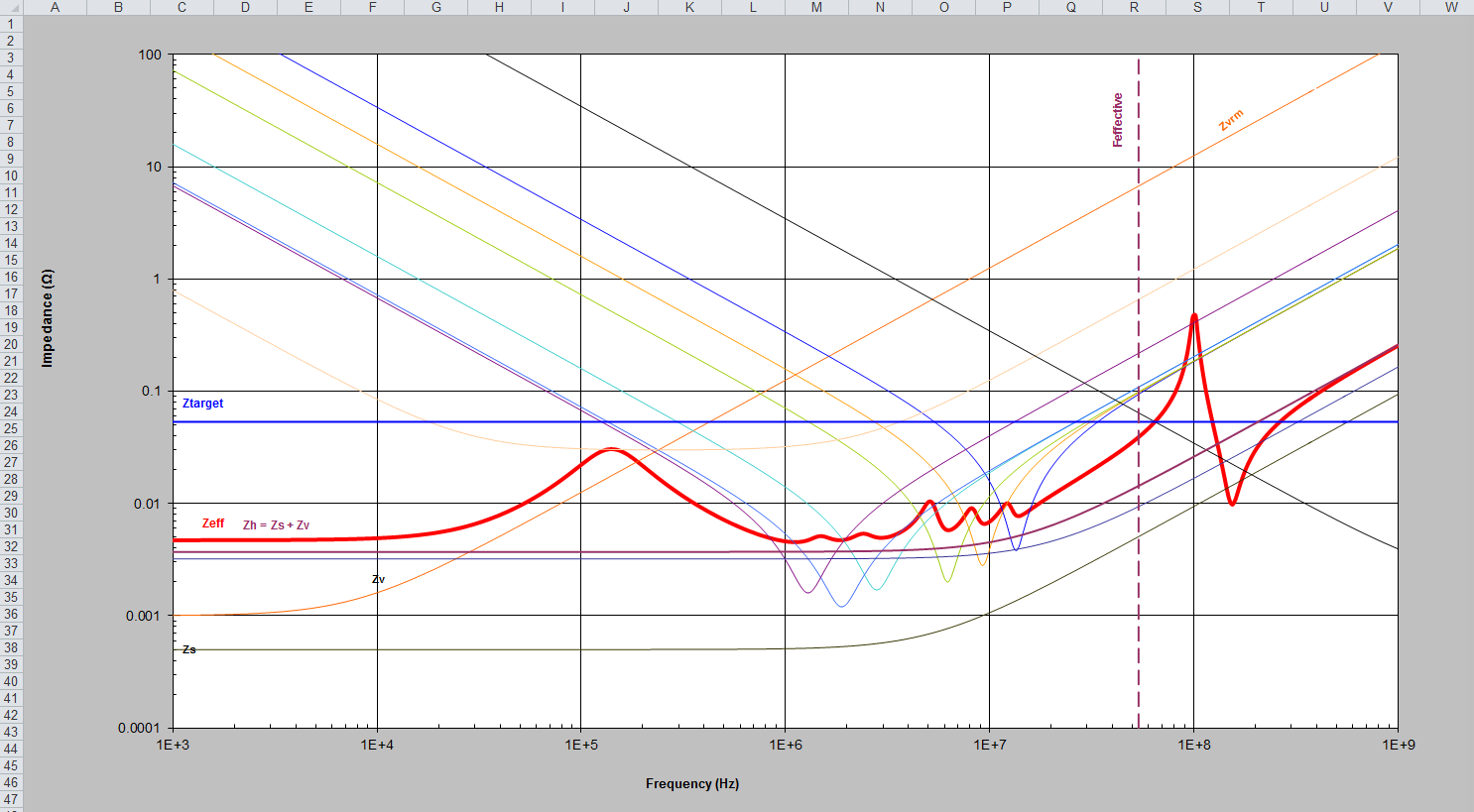

Step 5: Check the logarithmic graph (vertical axis: impedance, horizontal axis: frequency) on the PDN tool and adjust the number of capacitors so that the Zeff value meets the specifications.

By using the PDN tool provided by Intel, you can easily calculate the approximate capacity, number, and shape of decoupling capacitors, and use it to design power supply circuits for applications that incorporate FPGAs. You can achieve

- Check out the video below for an example of how to configure the PDN tool YouTube video