This Quartus® Guide series is for users of the Intel® Quartus® Prime design software.

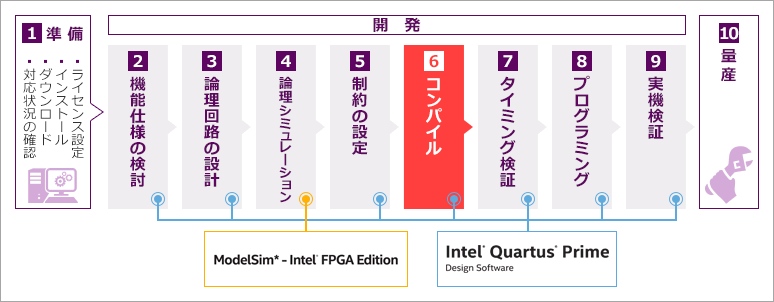

See here for FPGA/CPLD development flow.

explanation

This document will be helpful in the "6. Compilation" phase of FPGA/CPLD development.

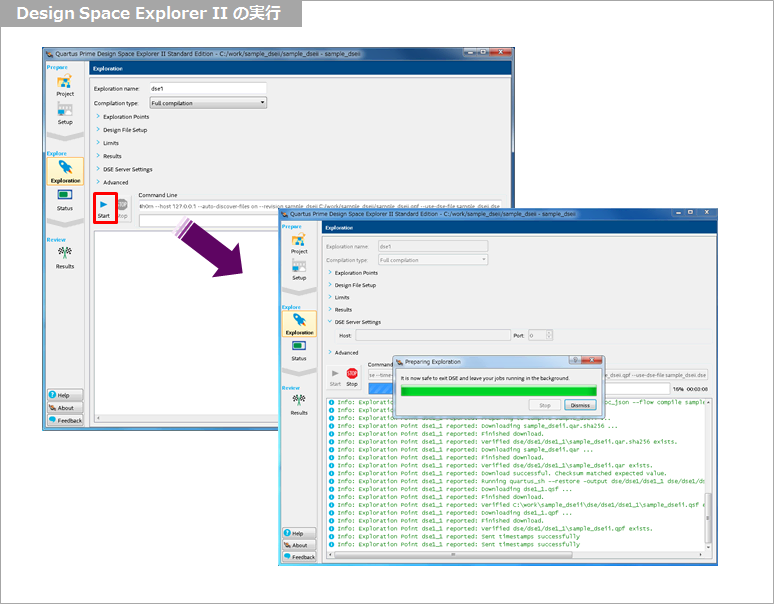

Design Space Explore II (DSE II) is a tool that automates the process of performing multiple compilations while changing Quartus® Prime optimization settings. DSE II enables efficient design optimization.

This document introduces the settings for running DSE II and how to check reports after running.

Document

Click here for recommended articles/materials

Quartus® Prime related articles and resources

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Click here for recommended seminars/workshops

Quartus® Prime Introductory Trial Course <Free>

Custom microcomputer design trial ~Experience embedded design using MAX® 10 FPGA! ~ <free>