Recent Intel® FPGAs naturally support external memory interfaces such as DDRx (External Memory Interface / EMIF), right? By the way, EMIF is called "Eimifu" by Intel® FPGA people.

What is the first thing that comes to your mind when thinking about implementing a memory controller on an Intel® FPGA?

- What FPGA devices does it support?

- What memory standards does it support?

- What transfer rate does it support?

Etc. I think there's a lot of things to worry about.

This page introduces the flow from selection to operation check, using a DDRx SDRAM controller as an example, for those who realize EMIF with Intel® FPGA for the first time.

Checking EMIF Support Status

Here is a useful page to check the EMIF support status of Intel® FPGAs.

- 外部メモリ・インタフェース (インテルのサイト 日本語版)

- External Memory Interface (インテルのサイト 英語版)

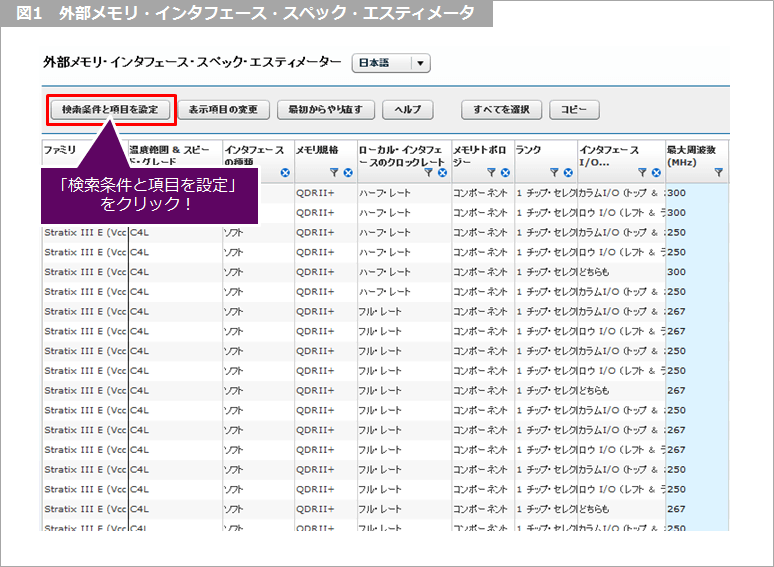

このページ内にある『外部メモリ・インタフェース・スペック・エスティメータ』を使用すると、インテル® FPGA の EMIF サポート状況を確認することができます。デバイス・ファミリやスピード・グレード、インタフェースの種類、メモリ規格、周波数など、いろいろな条件を入れて検索することができます。(2019年10月現在、日本語版のページから外部メモリ・インタフェース・スペック・エスティメータへのリンクが切れていますので、英語版のページからアクセスしてください。)

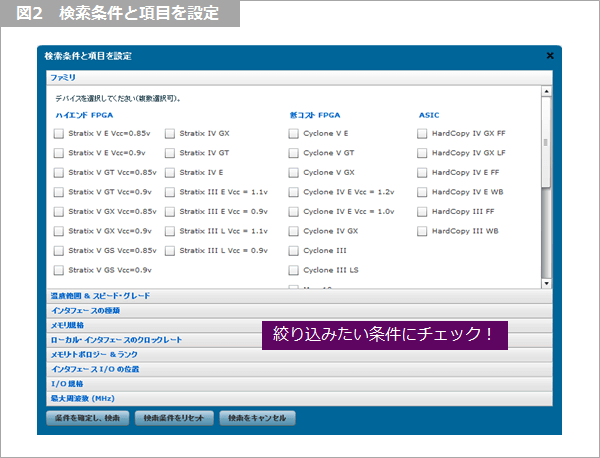

When you click "Set search conditions and items", the following setting screen will appear.

I think that it is better to specify it in a range that you can understand roughly without setting too much at first, and then gradually add conditions to narrow it down.

family

Check the device family that you are using or has been nominated for. You can also check for multiple device families.

If not checked at all, all device families are included.

Temperature Range & Speed Grade

Check the temperature range and speed grade of the device.

<Temperature range>

The following temperature ranges exist. However, depending on the device, there are temperature ranges that exist and temperature ranges that do not exist, so please refer to the documentation of each device for details.

- Commercial temperature range (C product): Junction temperature 0 to 85°C

- Industrial temperature range (I product): Junction temperature -40 to 100°C

- Automotive temperature range (A product): Junction temperature -40 to 125°C

- Extended temperature range (E product): Junction temperature 0 to 100°C

- Military temperature range (M product): Junction temperature -55 to 125°C

<Speed Grade>

Device families determine which speed grades exist to some extent. See the documentation for each device for details.

Interface type

- soft

It implements a memory controller by consuming FPGA resources such as logic and internal memory. Often called a soft memory controller (SMC).

- hard

A memory controller that is pre-loaded as a hardware macro inside the device is used. Often called a hard memory controller (HMC).

- Hard HPS

It uses the memory controller onboard the Hard Processor System (HPS) of the SoC FPGA with an ARM* core.

memory standard

Select an external memory standard.

Local interface clock rate

If there is a designation in advance, please select it.

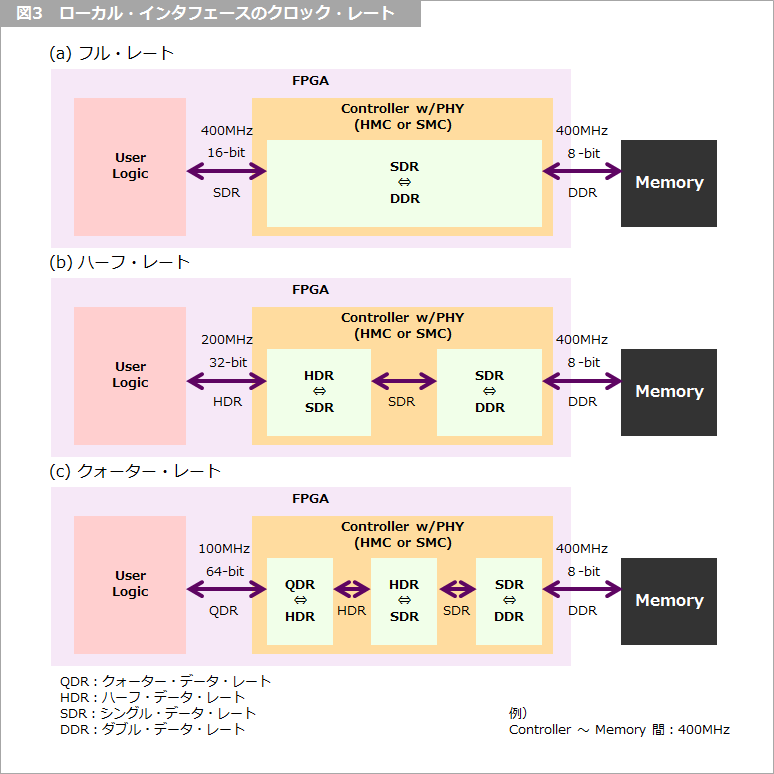

The image is shown below. (For ease of visualization, a double data rate of 400MHz (800Mbps) between controller and memory is used as an example.)

Simply put, data is transmitted between the controller and memory at high speed and at a double data rate. convert to However, at this time, the data width is doubled. This is the full rate.

Then, if at full rate the frequency is too high to process the data in the FPGA, halve the frequency further. However, at this time, the data width is doubled. This is the half rate.

Furthermore, if the frequency is too high even at half rate to process the data in the FPGA, halve the frequency further. However, at this time, the data width is doubled. This is the quarter rate.

Memory Topology & Rank

This item first selects the memory topology. Broadly select either components (memory devices) or modules (DIMMs), and in the case of DIMMs, select which type of DIMM.

For DIMMs, select which rank of DIMM.

For components, specify the number of chip selects.

Location of interface I/O

This item specifies in which bank of the FPGA the EMIF-related pins are placed. Some FPGAs support different transfer rates depending on the I/O bank location.

I/O standard

Select the I/O Standard for the memory interface.

Maximum frequency (MHz)

Specifies the upper and lower frequency limits for the memory interface (memory controller to memory).

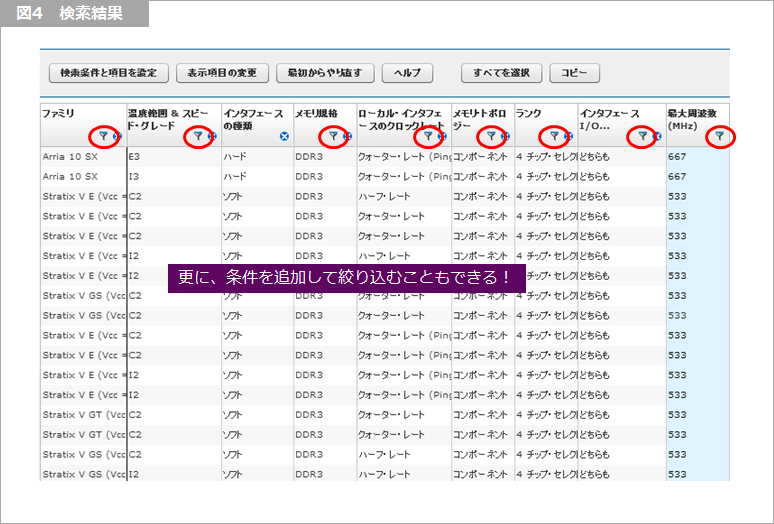

search results

Click "Confirm criteria and search" to display the results that meet the specified criteria. Even after the results are displayed, you can further narrow down by specifying conditions.

From this result, we have identified candidates for the FPGA to be adopted for the external memory interface section, so consider the FPGA to be used in consideration of other interfaces, conditions and specifications.

detailed information

- External Memory Interface (Intel site)

======================================

Practice

As a practical part, we will introduce how to generate and simulate a memory controller to be implemented in Intel® FPGA, and how to check operation using a development kit.

DDR4

DDR3

Design & Debug Guidelines

As the speed of the external memory interface (EMIF) increases, the shrinking data valid window (effective window of data) and the deterioration of signal quality are being raised as issues.

As the amount of time spent on verification and debugging to meet the required specifications tends to increase, it is important to design device boards according to appropriate procedures and implement methods for debugging in advance at the design stage.

This document presents the design flow and debug flow, and aims to solve problems quickly by preventing bugs from entering and implementing the mechanism necessary for debugging by designing in an appropriate procedure. it was created.

EMIF Design & Debug Guidelines for FPGAs

Click here for recommended articles/materials

DDR3 works on Intel® FPGA! (Practice version) [1/2]

DDR3 works on Intel® FPGA! (Practice version) [2/2]

DDR4 works on Intel® FPGA! (Practice version)

EMIF Design & Debug Guidelines for FPGAs

Intel® FPGA Development Flow/Top Page