This Quartus® Getting Started Guide series is for users who are new to the Intel® Quartus® Prime / Quartus® II development software.

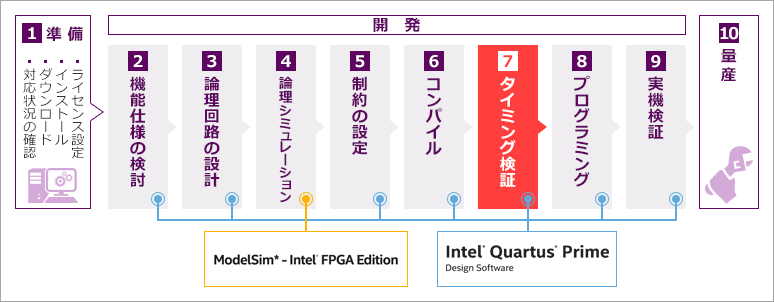

See here for FPGA/CPLD development flow.

explanation

This document can be used as a reference in the "7. Timing Verification" phase of FPGA/CPLD development.

Describes the methods used in the Quartus® Prime/Quartus® II software to ensure that the placed and routed results meet the timing constraints.

This document describes how to read the report of the TimeQuest Timing Analyzer, which is used to confirm whether the placement and routing result satisfies the timing constraints when compiling with timing constraints for the FPGA/CPLD design (circuit). I'm explaining.

Document

quartus-hg_timing-analysis_v1710_r1__1.pdf

"Quartus Prime Beginner's Guide - Timing Analysis Method by TimeQuest ver.17" (Document for tool version: Ver.17.1)

"Quartus II Beginner's Guide - TimeQuest Timing Analysis Method ver.15" (Document for tool version: Ver.15.0)

"Quartus II - How to Read and Analyze TimeQuest Timing Analyzer Reports Quick Guide ver.13" (Document for tool version: Ver.13.0)

Click here for recommended articles/materials

Quartus® Prime related articles and resources

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Click here for recommended seminars/workshops

Quartus® Prime Introductory Trial Course <Free>

Custom microcomputer design trial ~Experience embedded design using MAX® 10 FPGA! ~ <free>