This Quartus® Getting Started Guide series is for users who are new to the Intel® Quartus® Prime / Quartus® II development software.

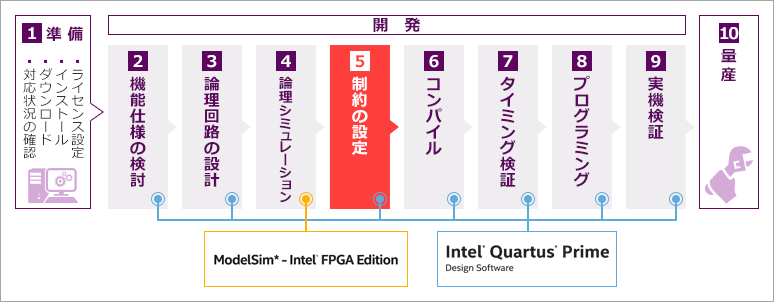

See here for FPGA/CPLD development flow.

explanation

This document can be used as a reference in the "5. Constraint Setting" phase of FPGA/CPLD development.

Introduces how to apply timing constraints to the target FPGA/CPLD design (circuit) with the Quartus® Prime / Quartus® II development software.

This document explains how to create a timing constraint file (SDC file) used when applying timing constraints to FPGA/CPLD designs (circuits). Originally a standard format for the ASIC industry, Synopsys Design Constraints (SDC) files are used for FPGA/CPLD timing constraints to guide the Fitter in the Quartus® Prime/Quartus® II development software. ) as well as for high performance timing analysis with the TimeQuest Timing Analyzer.

Document

Quartus® Prime Getting Started Guide - How to Constrain Timing with TimeQuest ver.17

(Tool version: Document for Ver.17.1 (Rev.2)

Quartus II Getting Started Guide - How to Constrain Timing with TimeQuest ver.15

(Tool version: Document for Ver.15.0 (Rev.2)

Click here for recommended articles/materials

TimeQuest - Timing Analysis Terms and Concepts -

Quartus® Prime related articles and resources

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Click here for recommended seminars/workshops

Quartus® Prime Introductory Trial Course <Free>

Custom microcomputer design trial ~Experience embedded design using MAX® 10 FPGA! ~ <free>