Intel: When ALTPLL IP is RTL simulated on Questa* - Intel® FPGA Edition, the waveform of output clocks (such as c0) is indeterminate. why?

Category: Simulation

Tools: Questa* - Intel® FPGA Edition

device:-

This happens when the ALTPLL IP is created in VHDL and the Questa* - Intel® FPGA Edition simulation is run manually (GUI or command).

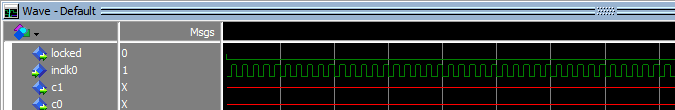

To successfully run the ALTPLL IP simulation model, the resolution specified during simulation must be less than ps (1ps). (A higher resolution rounds calculations, resulting in incorrect multiplication or division.)

To work around this issue:

For GUI operation

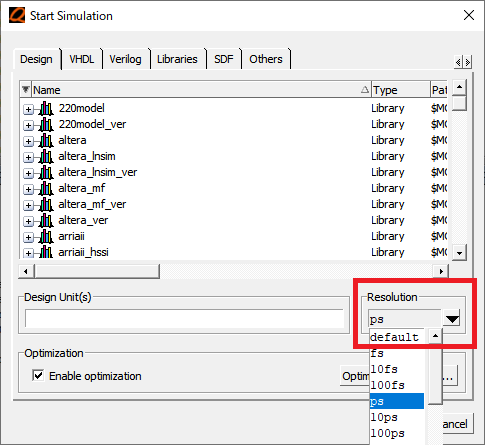

When running with Start Simulation,

Change the Resolution located at the bottom right of the [Design] tab to a value smaller than ps and the unit, and run the simulation.

For command operation

Add the option -t to specify the resolution to the vsim command and specify the unit.

<Example: Specify 1ps>

vsim -t 1ps -L altera_mf … (Omitted below)

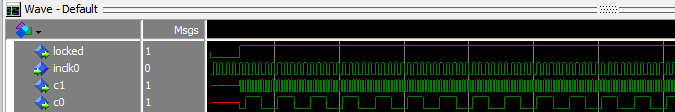

By specifying a resolution smaller than 1 ps, the output clock waveform of the ALTPLL IP is generated.

Note that when running in NativeLink simulation, the resolution will be set to 1ps, so

This event does not occur.

![]() Experienced FAE

Experienced FAE

Free consultation is available.

From specific product specifications to parts selection, the Company FAE will answer your technical concerns free of charge. Please feel free to contact us.