Introduction

This article is a Japanese translation of a blog post published on the Skyworks website.

There are many technical articles about clocks, but this first one touches on "Clock trees and how to calculate jitter."

If you're interested, be sure to read the original Skyworks blog post.

What is a Clock Tree?

Clocks are inseparable from jitter, which affects signal quality.

Furthermore, when there are multiple clock ICs in a system and a large number of clock outputs, it can be difficult to imagine how jitter will manifest itself and how it will affect the clock signal.

There are clock ICs called jitter cleaners (also called jitter attenuators) that reduce jitter in the reference clock.

This article will explain when you need a jitter cleaner and how to calculate jitter in the first place.

Applications that require multiple clock distribution within a data center, communication base station, or system require

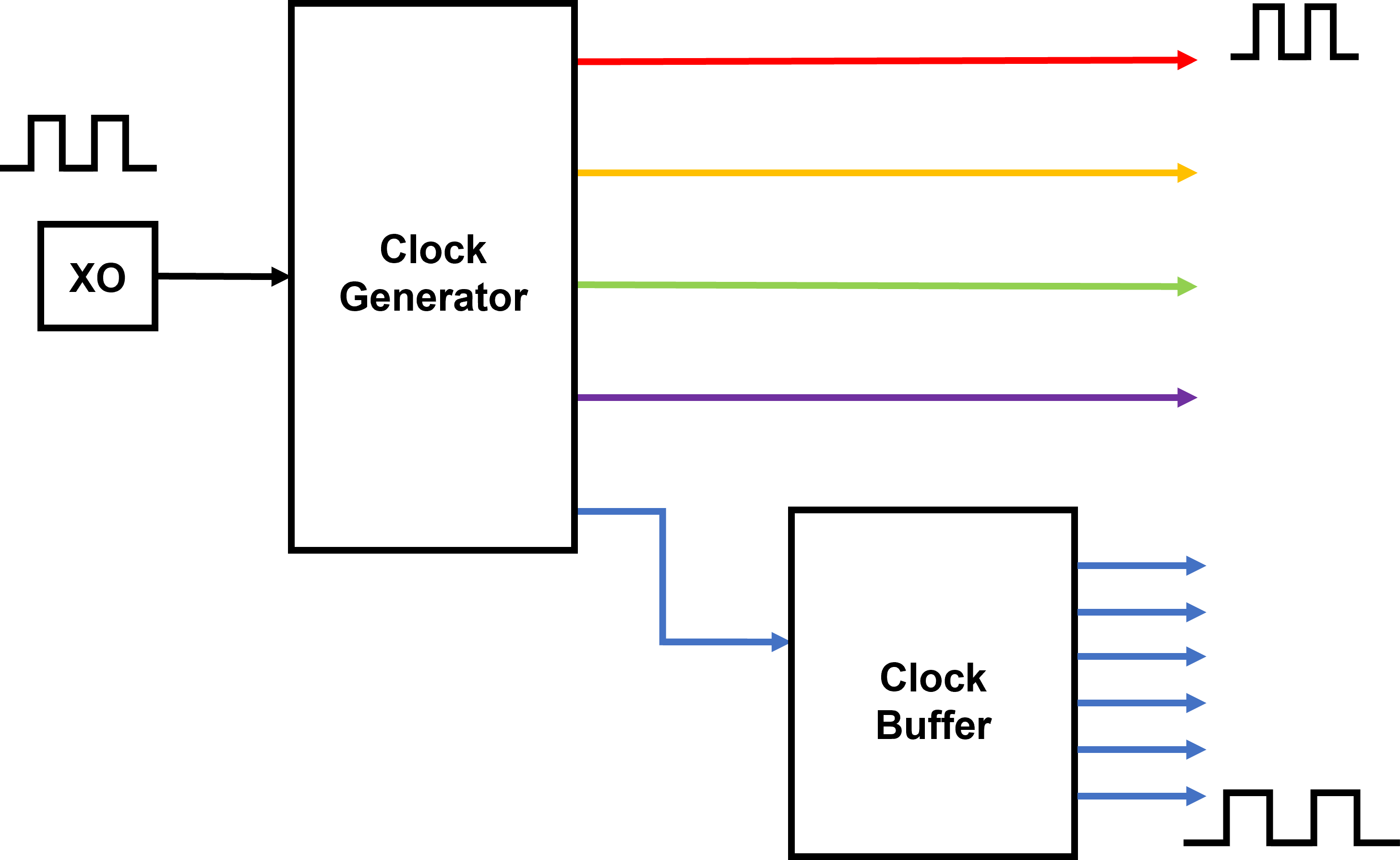

It typically consists of a quartz crystal or a low jitter XO (crystal oscillator) connected to a clock generator, followed by one or more buffers.

A clock device configuration with such a series of connections is called a clock tree.

The following diagram is an example of a clock tree configuration.

Calculate the total jitter from the clock tree

In this example, the clock is sourced from a low-jitter XO, which determines the frequency stability of the entire clock tree.

The clock generator then produces several different output frequencies based on the input frequency from the XO.

Finally, a clock buffer takes one of these output frequencies and distributes (replicates) multiple output clocks of the same frequency.

*The colored arrows in the diagram indicate different clock frequencies.

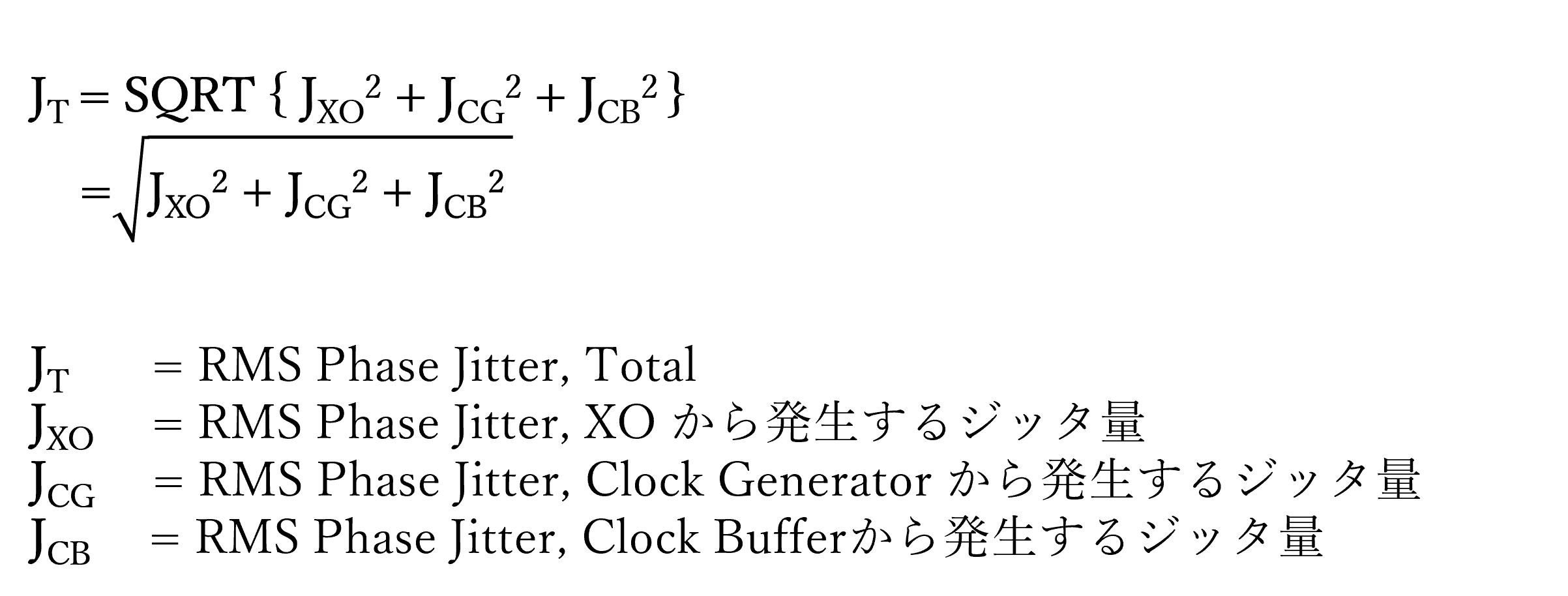

It might seem that the jitter of the clock at the end of the clock tree can be found by adding up the jitter components of each clock IC, but this cannot be found by simple addition.

An effective way to evaluate jitter is to analyze the jitter components of each clock in the frequency domain rather than the time domain.

The phase noise of each clock IC is measured at each offset frequency and then integrated over a specific band (e.g., 12kHz to 20MHz).

The integrated result is expressed as RMS jitter,

By taking the square root of the sum of the squares, we can estimate the total jitter of the clock at the end of the clock tree.

In the above example, the total RMS phase jitter can be estimated as:

Example of a noisy clock source

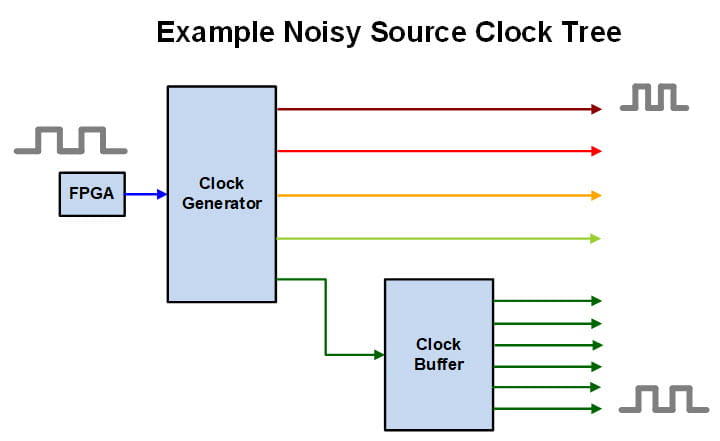

The clock tree example assumes that the clocks come from a low-noise source, which is not the case for all clock trees.

In reality, it may be regenerated from serial data or even created from an FPGA.

Also, the board itself may be introducing power supply noise to the XO.

In such a case, the clock tree will behave as shown in the figure below, resulting in large jitter. To indicate this, the waveform is drawn thicker than in the previous figure.

Reduce jitter with Jitter Cleaner!

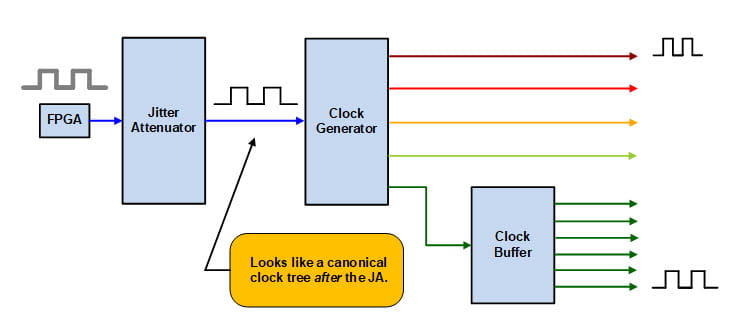

To improve a noisy clock tree, a jitter cleaner is needed to remove noise from the source clock and improve the jitter performance of the entire clock tree.

In the diagram below, a mechanism is introduced to clean up the clock by inserting a jitter cleaner between the noisy FPGA-derived source clock and the clock generator.

Unlike the previous diagram, after passing the clock tree through the jitter cleaner, it behaves the same as a clock tree with less noise.

Actual clock ICs not only reduce jitter but also allow frequency setting, and often a single device acts as both a jitter cleaner and a clock generator.

Skyworks Jitter Cleaner Lineup

Skyworks Jitter Cleaner has low jitter performance and generates low jitter, high precision clock signals even from noisy clock sources.

Skyworks' proprietary DSPLL (Phase Locked Loop) technology enables very fine output frequency setting with low jitter, minimizing jitter throughout the clock tree.

This supports stable operation even in applications with strict timing requirements, such as data centers, communications infrastructure, and industrial equipment.

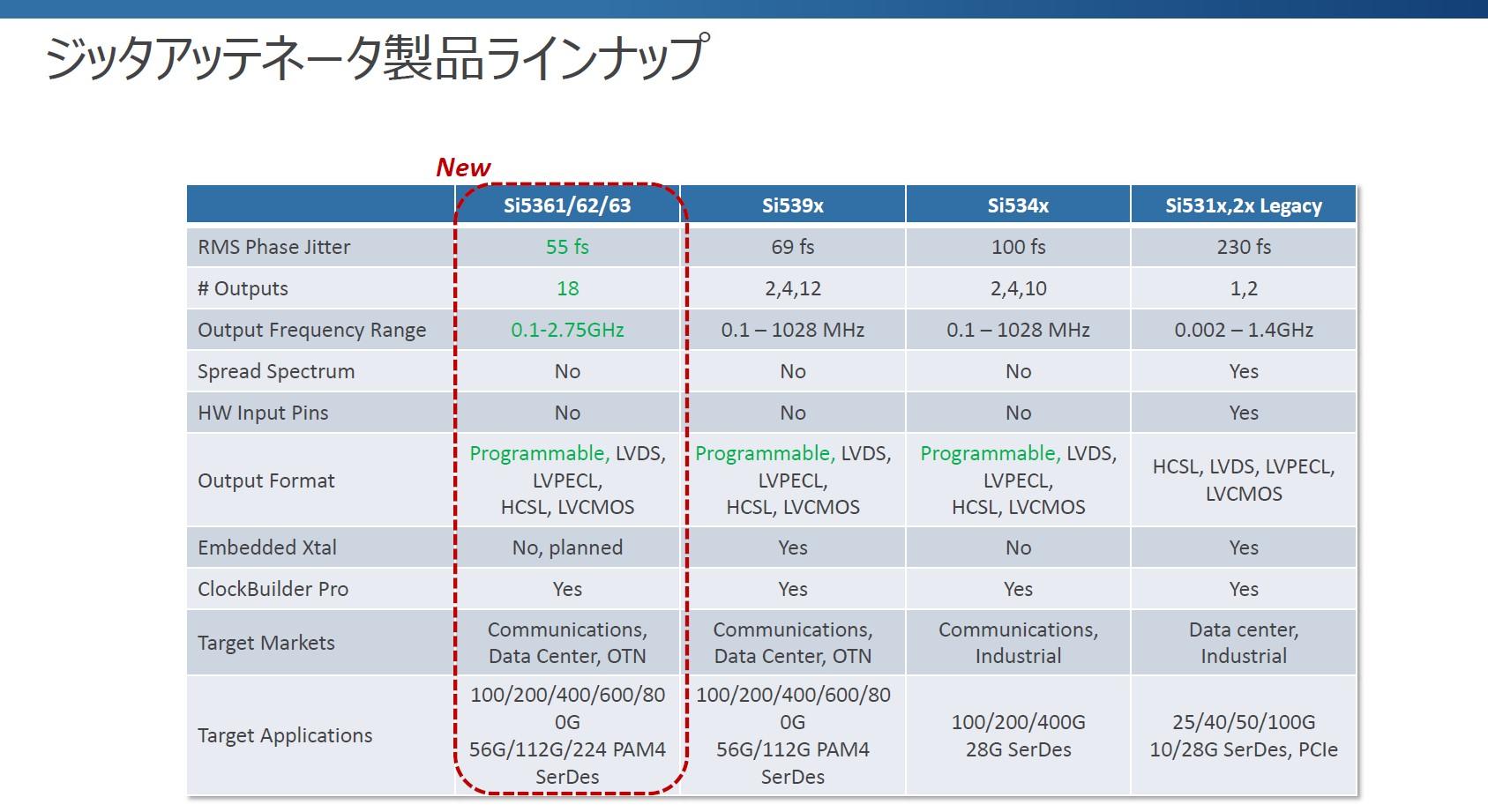

Skyworks' Jitter Cleaner lineup is as follows:

Summary

The method for calculating jitter varies depending on the type of jitter, but in general, analysis in the frequency domain is effective for evaluating phase jitter.

RMS phase jitter is calculated from the phase noise at each offset frequency and is important for analyzing the frequency components of jitter in a clock signal and for separating and understanding the effects of low-frequency and high-frequency components.

By understanding how much jitter occurs through the clock source, clock generator, and buffer, and using a jitter cleaner,

It is important to verify that the final output result meets the required jitter performance.

I hope this article was helpful.

Related article

If you are interested in Skyworks' low-jitter clock ICs, please also read the article below.

[DL available] SKYWORKS timing products and complete lineup information

To Skyworks manufacturer information Top

If you would like to return to the Skyworks manufacturer information top page, please click below.