SiC cascode JFET in a surface-mount TOLL package that achieves low on-resistance and reduced mounting area

ON Semiconductor has expanded its groundbreaking Gen 4 SiC cascode JFET portfolio with a new product in a surface mount TO-Leadless (TOLL) package. This product is the first in the family of 750V SiC cascode JFETs released in a TOLL package, with on-resistances ranging from 5.4mΩ to 60mΩ. These products are ideal for use in space-constrained applications such as AC/DC power supplies from hundreds of watts to several kilowatts, as well as solid-state relays and circuit breakers up to 100A levels.

In the 600/750V class of power FETs, Gen 4 SiC cascode JFETs offer superior performance in terms of on-resistance and output capacitance figures of merit (FOM). In addition, the 5.4mΩ product in a TOLL package achieves 4-10x lower on-resistance than competing Si MOSFETs, SiC MOSFETs, and GaN transistors. The 750V rating of the SiC cascode JFET is also 100-150V higher than alternative technologies, allowing for significantly improved design margins for managing voltage transients.

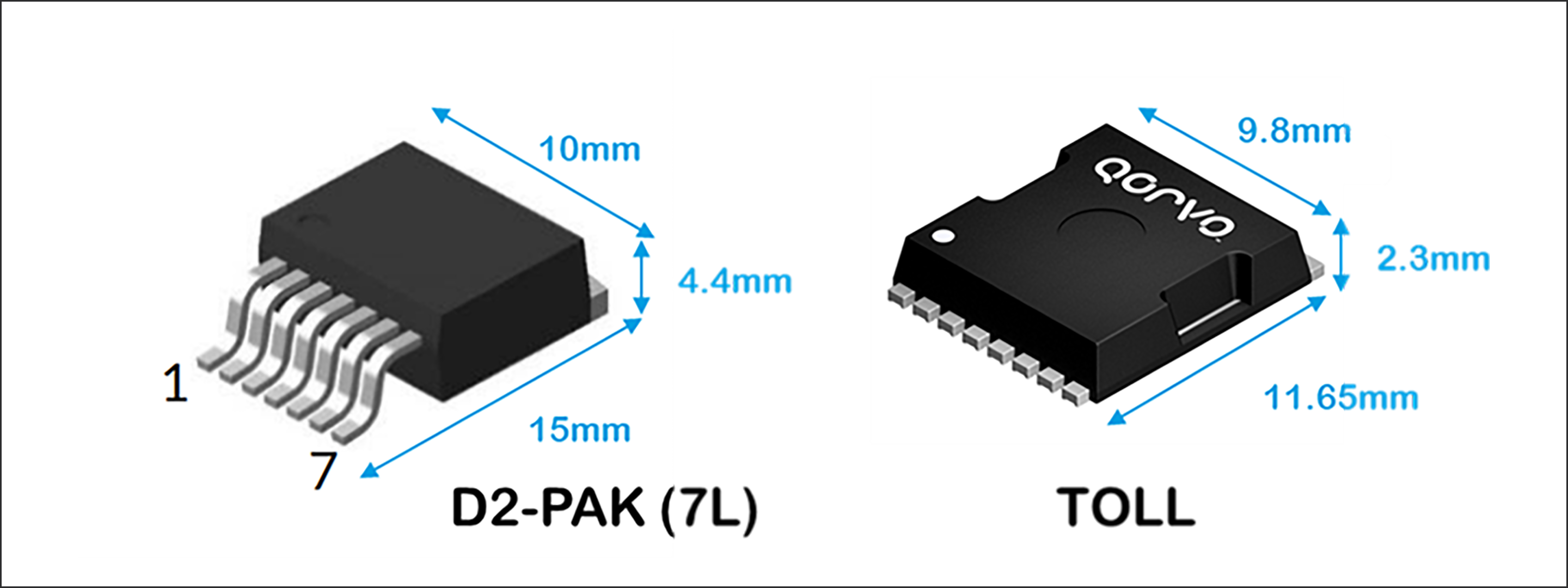

The TOLL package has a 30% smaller footprint and half the height of 2.3mm compared to the D2PAK surface mount product. The TOLL package also allows a Kelvin source connection for cleaner gate waveforms for reliable and fast switching of high currents.

This SiC cascode JFET is a product that combines SiC JFET and Si MOSFET in ON Semiconductor's unique cascode circuit configuration to improve efficiency with wide bandgap switch technology and simplify gate drive of silicon MOSFET. Ultra-low on-resistance in a small TOLL footprint is achieved by ON Semiconductor's SiC cascode JFET technology's world-leading on-resistance x area (R DS(On)x A) and best-in-class figure of merit (FOM).

Despite the significant size reduction, advanced manufacturing technologies such as sintered die attach have achieved the industry's highest level of thermal resistance from the junction to the case of 0.1°C/W. The 750V/5.4[mΩ] UJ4SC075005L8S has a continuous current rating of 120A up to a case temperature of 144°C and a pulse current rating of 588A up to 0.5ms.

Ultra-low on-resistance, high T j,max =175℃ Combined with excellent transient thermal behavior, Silicon MOSFET More than about 8 Twice as good I 2 t This provides high-performance, high-voltage, high-voltage, high-power, and low-power ratings, making the design easier while increasing robustness and resistance to transient overloads. 4 teeth, TOLL Packaged in S and SiC cascode JFET In this example, the maximum pulse current and pulse width are shown. FET teeth PCB Thermal vias, insulating thermal interface material, T HS =50℃ The model is assumed to have a heat sink that is maintained at 1000 Hz (R th,c-hs =1.4 ℃ /W The steady-state thermal resistance from the junction to the heat sink is 1s Under a pulse exceeding FET In this region, the rated current of the SiC cascode is limited. JFET is high T j,max, low on-resistance, low thermal resistance 2 This represents a major advantage in current handling, more than double the current.

However, for short pulse widths dominated by the transient thermal impedance of the semiconductor material, die attach, and lead frame, much larger transient overcurrents (maximum continuous currents) are possible. 4-6 On Semiconductor's new TOLL SiC Cascode JFET teeth, Silicon Carbide Excellent heat resistance, advanced Ag-sinter Die attach, 175℃ It provides excellent surge current performance by utilizing a maximum junction temperature of 1000 Ω and ultra-low on-resistance at high current density. 4 In the example, SiC cascode JFET The maximum overcurrent of the Silicon MOSFET (t p ~0.5ms-1ms)twist 2.8 has been shown to be 2 times higher.

The low conduction losses, small size, high surge ruggedness, and excellent turn-off capability of this new ultra-low on-resistance TOLL part make it ideal for often thermally demanding protection applications in small enclosed spaces where active cooling is not available. has become a good candidate. It also reduces the need to parallel multiple FETs, minimizing heat sinking.

Inquiry / Quotation

If you have any questions about this product or would like a quote, please contact us below.

On Semiconductor Manufacturer Information Top Page

If you want to go back to ONSEMI maker information top page, please click below.