Ask a power converter designer what they want from a semiconductor switch and you might get the answer: “Low on-resistance, high off-resistance, and the fastest possible transition between the two states.” Of course, in simple terms, this translates to low power consumption. ON Semiconductor’s SiC cascode JFETs come close to this ideal, with on-resistances of less than 6mΩ in the 750V class, edge rates in the nanosecond range, and efficiencies of over 99.5% in multi-kW converters and inverters.

Designers will want to throw in a few extras: easy gate drive, high voltage rating, efficient third quadrant operation, high avalanche energy and short circuit ratings, low thermal resistance, low system cost, etc. Luckily, SiC cascode JFETs have these covered too, with best-in-class figures of merit.

But running a SiC cascode JFET at its maximum slew rate on a breadboard quickly put it in smoke. "The supply voltage was well below its maximum and the load was light." So how much wiring and connection inductance was there? Just 100nH of inductance, with a staggering current edge rate of 3000A/µs, would generate a 300V voltage spike, according to the familiar equation V = -L*di/dt, stressing the switch. It induced high frequency ringing for a short time before the SiC cascode JFET broke.

We now know that unless we eliminate the connection inductance or significantly over-spec the switch voltage rating and use extensive EMI filtering, we need to control the edge rate to dampen the ringing. The traditional way to suppress voltage spikes has been to add a gate resistor RG(OFF) in series, but this is problematic and introduces a delay into the waveform, limiting the duty cycle and high frequency operation that are one of the greatest advantages of wide bandgap switches. Also, the gate resistor greatly increases the losses in the switch and does little to dampen the ringing.

A better solution is a simple RC snubber. You might shy away from the large, hot resistor-capacitor networks typically required for IGBTs, but not for SiC cascode JFETs. Snubbers are primarily used to damp resonances between the connection inductance and the capacitance of the device, but the capacitance of SiC cascode JFETs is very small. This means that a capacitance of around 200 pF (2 or 3 times Coss(er)) and a few ohms of series resistance is generally sufficient to provide sufficient damping. Some power is dissipated in the snubber resistor, but the network serves to reduce the overlap of switch-off voltages and currents in both hard- and soft-switched applications, so in practice this transition is less lost.

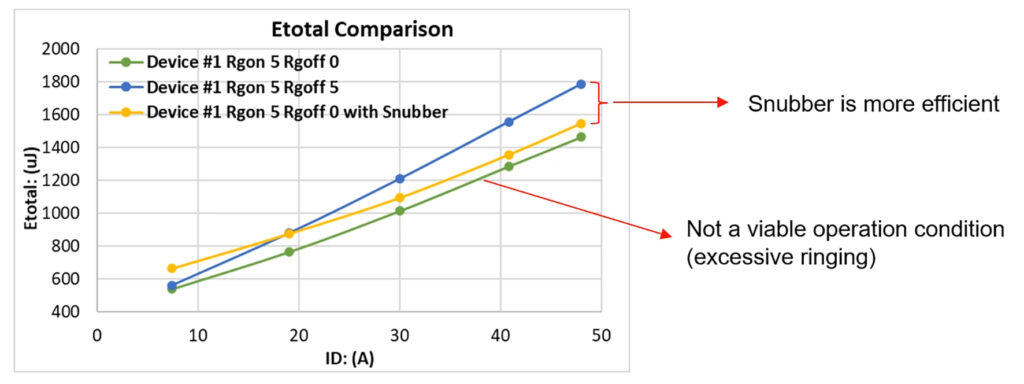

The snubber does incur some loss at turn-on, so to get the full picture the total loss E(ON)+E(OFF) must be considered. The figure shows E(TOTAL) for 40mΩ. The blue line is without the snubber, with RG(ON) and RG(OFF) both at 5Ω. The yellow line is with RG(ON) at 5Ω, RG(OFF) at 0Ω and a 200pF/10Ω snubber. Using the snubber at 40A has a clear net benefit of reducing losses by about 10.9W when operating at 40kHz. At light loads the situation is reversed, but at these levels the losses are small.

The energy absorbed by the snubber resistor in a typical application is estimated to be about 120 μJ per cycle, which corresponds to about 5 W at 40 kHz. However, evaluation shows that most of this energy is not dissipated by the snubber resistor, but rather by the SiC cascode JFET channel passing through its linear region at turn-on. As a result, a 1 W resistor is usually sufficient for the snubber, and surface mount resistors can easily be used at this power level. The capacitor can also be made small.

Designers can easily and inexpensively adjust by adding a snubber circuit to reduce overshoot and ringing without sacrificing other benefits.

Inquiry

If you have any questions regarding this article, please contact us below.

On Semiconductor Manufacturer Information Top Page

If you want to go back to ONSEMI maker information top page, please click below.