SiCカスコードJFETの温度によるパラメーターの変化を考えてみる

パワートランジスターには、ドレイン-ソース間抵抗Rdsやスイッチング損失Eossなど、いくつかの重要なパラメーター(FoM)があります。これらの数値は通常、データシートに記載されていますが、これらの数値が温度によってどのように変化するかは必ずしも明らかではありません。また、これらの数値はダイの面積にも影響され、RdsAや面積に対するRdsなどのFoMが発生します。

もちろん、これらの数値は「代表値」であり、一般的には動作温度25℃の場合に示されています。また、これらの数値は、これらの「典型的な」条件でのRds(on)から得られたものであり、Rds(on)が温度によってどのように変化するか、さらに重要なことに、その変化がアーキテクチャーによってどのように異なるかを考慮していません。

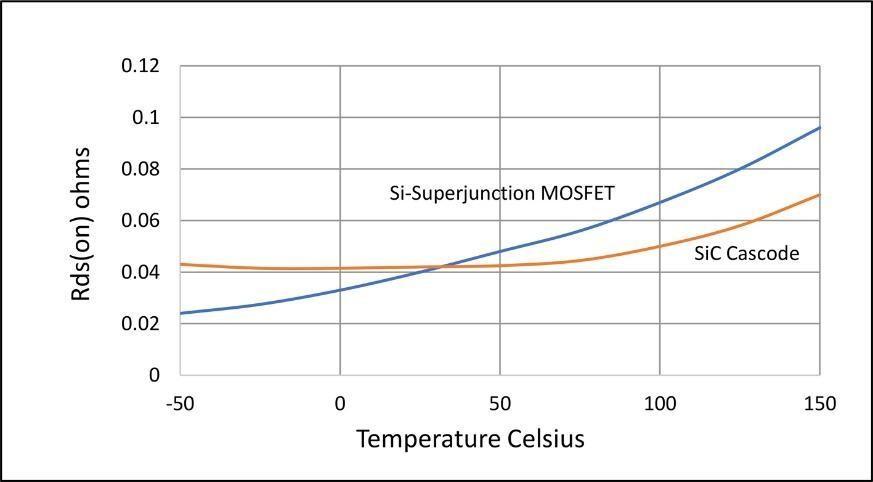

このことは、オンセミ社の650V SiCカスコードJFETデバイス「UF3C065040K3S」などを見るとよくわかります。このデバイスは、25℃でのRds(on)が最大52mΩ(標準42mΩ)であると記録されています。これを、Rds(on)が45mΩ max (40mΩ typical)の650VスーパージャンクションMOSFETと比較すると、この特定のFoMではスーパージャンクションデバイスの方が優れた性能を発揮しているように見えます。しかし、図1が示すように、温度が上がると状況は大きく変わります。150℃に近づくと、スーパージャンクション素子のRds(on)は96mΩに達しますが、SiCカスケード素子では78mΩにとどまります。実際、175℃でもSiCデバイスのRds(on)は78mΩにとどまり、スーパージャンクションデバイスのRds(on)を大きく下回っています。

図1から明らかなのは、SiCカスケード素子のRds(on)の増加率が、スーパージャンクションMOSFETよりもはるかに低いということです。

この伝導損失の低さに関連して、SiCカスコードJFETは高温での消費電力が少なくなり、150℃でのスーパージャンクションデバイスに比べて30%もの消費電力の低減が可能になる。放出される電力量は温度の上昇にも寄与するため、損失が少ないということは全体の温度が低いことを意味し、したがってRds(on)の数値もさらに低くなります。また、Rds(on)が低いということは、より大きな電流を流すことができるということでもあり、これらのデバイスが使用されるアプリケーションにおいては、さらに大きな意味を持ちます。このFoMのもう一つの利点は、ダイ面積を最小限に抑えることができるため、スイッチング損失やボディーダイオード損失を低減できることです。

SiCカスコードJFETの温度に対するRds(on)の増加率が低いのは、SiCで使用されているドーピングレベルが高いことによる特長です。これにより、すべての半導体材料で温度上昇に伴って増加する電子移動度の低下が緩やかになります。さらに、ゲートチャージやその他のFoMの面でもメリットがあり、エンジニアは、SiCカスコードJFETを使用することで、システムレベルでの設計の大幅な改善とコストの削減が可能になることを理解できるでしょう。

データシートは、あるデバイスがさまざまな条件でどのように動作するかを示してくれますが、温度による影響を理解し、異なるタイプのデバイスを一概に決めつけないことが重要です。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミメーカー情報Topページへ

オンセミメーカー情報Topページへ戻りたい方は、以下をクリックください。