PCIe Switch (PCIe SW)

Peripheral Component Interconnect express (PCIe for short). I'm sure many of you have seen this name on motherboard connectors. Do you know a PCIe Switch (PCIe SW for short) that uses this standard?

PCIe was originally a standard for accessing memory from the CPU, but now it is often used for servers and storage. In addition, even industries that were not interested in high-speed communication are now showing increasing interest in high-speed communication due to the advent of high-precision cameras and 5G, as the amount of data increases. In this article, we will explain in order while focusing on the basic functions and features of PCIe SW.

Preliminary knowledge about PCIe

Before starting the explanation of the function and configuration of the main topic, I will add a little bit. Since PCIe SW is a communication standard, the communication speed is defined for each generation. Gen1 = 2.5, Gen2 = 5.0, Gen3 = 8.0, Gen4 = 16.0, Gen5 = 32.0Gbps, and there is also talk that the development of Gen6 = 64.0Gbps is in progress. Inquiries about Gen3 and Gen4 are centered on Microchip 's PCIe SW. There are detailed performance differences for each Gen, such as "number of supported lanes (24, 68, etc.)" and "does it support FW customization?", so it is possible to provide products that meet customer needs. An example of the page link of Microchip 's PCIe SW products is described at the bottom of this page, so if you are interested, please check from there.

About Root Complex (RC) and Endpoint (EP) of PCIe SW

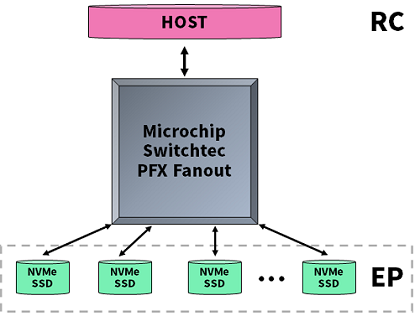

In the first installment, we will explain RC (Root Complex) and EP (Endpoint), which are the most basic devices using PCIe SW. PCIe SW is centered on the function of distributing (switching) data sent from the host to downstream end devices. The Host at this time is recognized as RC, and the End device as EP. (Refer to the figure below)

After the PCIe SW receives the data thrown by RC, it is transmitted to each EP while switching appropriately. Of course, there should be no packet loss or garbled packets, so PCIe SW also has a function to protect packets.

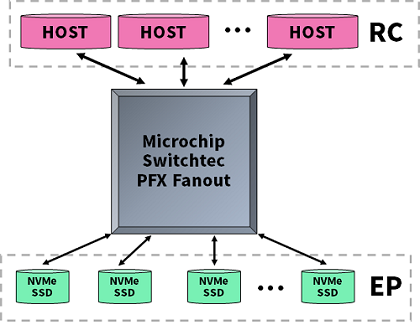

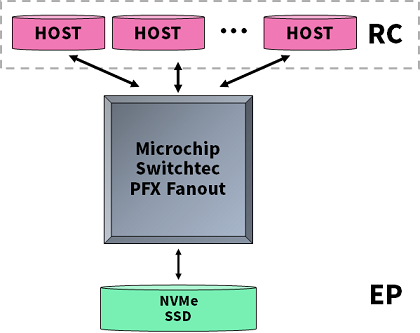

Also, PCIe SW can have multiple RCs and EPs for one PCIe SW. The PCIe SW manufactured by Microhip that we handle enables access from RC to other RC, and is excellent in convenience such as ensuring redundancy by controlling between RCs. Considering that RC is used for CPU and EP is used for SSD, PCIe SW is used when distributing data at high speed to multiple (or single) SSDs for a single or multiple CPUs. It means to use. (Refer to the figure below)

In the first installment, I briefly explained RC and EP of PCIe SW. In the second article, I will explain Memory space and Config space of PCIe SW.

Manufacturer product page link

Inquiry

If you have any questions regarding this article, please use the button below.

To Microchip manufacturer information Top

If you want to return to Microchip manufacturer information top page, please click below.