Utilization of bridges for high-speed implementation of multi-core CPUs

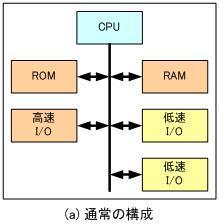

As you know, the higher the implementation rate of FPGA, the more difficult it becomes to increase the operating speed. Multicore CPUs are no exception. Therefore, before incorporating multi-cores, I will teach you one know-how for high-speed implementation of soft-core CPUs. Figure 3(a) is a general configuration when designing a module with a soft-core CPU. Memory and fast/slow I/O are all connected on one bus. Vendor support tools generate logic with all the hardware surrounding the CPU as a single module. If you are unfamiliar with this configuration, please refer to the previous explanation or the documentation provided by the vendor.

I/O modules are generally slower than CPUs, so there is no need to connect them to a high-speed bus. As more functions (I/O) are added, the logical scale of the module, including the CPU, increases, resulting in a decrease in the operating speed of the CPU. It is good if the target performance can be achieved with the configuration as it is, but if it cannot be achieved even by making full use of the tools, there is no choice but to modify the logic.

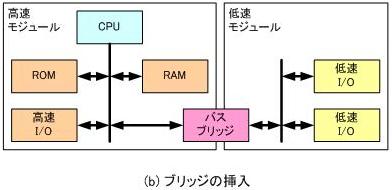

In that case, as shown in Fig. 3(b), I have adopted the method of dividing the high-speed and low-speed operation parts into modules and connecting them with a bus bridge. This is very common in SoC (System On Chip). Dividing into modules makes tuning easier, and high-performance logic can be realized while reducing development man-hours.

Figure 3 Separation of slow I/O by bridges

However, there is one problem with using a bus bridge. Since the bus bridge looks like one large address space from the CPU, the existence of the low-speed I/O beyond it is hidden. No standard function is generated to access it. As a countermeasure, create a project with the configuration shown in Figure 3(a) in which the low-speed I/O are located at the same address, and use that for software development. It may seem like double work, but it is more accurate and efficient than doing it manually, so please treat it as an essential work to achieve your target performance.

There are many things to consider when using a bus bridge, such as the handling of interrupts and burst transfers, but I will not discuss them here.

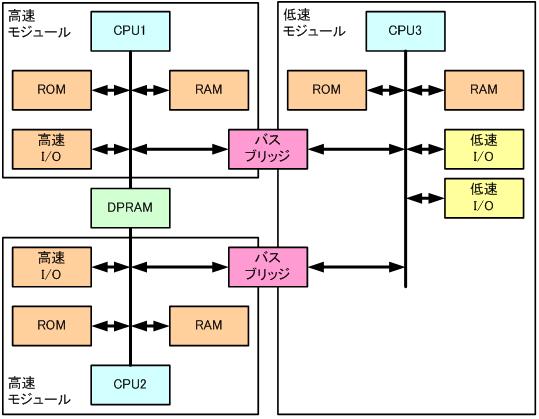

Figure 4 shows an example configuration with 3 CPUs using a bus bridge. DPRAM is used as shared memory for high-speed inter-module communication. A CPU is also mounted for low-speed I/O control, further reducing the load on high-speed modules. If you understand the explanations so far, you probably don't need a detailed explanation.

However, system design by distributing functions has a high degree of freedom and can be configured closer to the required specifications, but the basic design requires in-depth consideration. If you neglect this consideration and design too easily, there is a danger that the project itself will explode, so please be careful about that point.

Fig. 4 Example of functional distribution configuration with 3 CPUs

If the function can be distributed via this bus bridge, the CPU can be inside or outside the FPGA. In other words, the same configuration is possible even if one or all of the high-speed modules are commercially available microcontrollers. In other words, the flexibility of FPGA makes it possible to realize any system configuration.

in conclusion

I've explained the soft-core CPU from the hardware side, but did you find it interesting or would you like to try it? Dear System Designers! If you design the system you are currently in charge of from scratch without any restrictions, think about how much it will differ from the configuration you are currently using. Are you at the mercy of words such as diversion of assets and shortening of the design period, and are you designing away from the manufacturer's essence of providing truly good products for users?

The combination of a soft-core CPU and FPGA, which has a high degree of design freedom and can lead to solutions closer to the required specifications, is "the only option that can realize a user-oriented SoC from a single minimum order."

This time, we have finished talking about hardware, and we plan to move on to software next time.