~Welcome to the world of soft-core CPU with infinite possibilities~

Introduction

Last time, I explained how to design an FPGA with a CPU, and how to use Altera tools for Nios II. This time, I will focus on the concept of implementing a soft-core CPU, avoiding content that depends on tools.

single core or multicore

Needless to say, any number of soft-core CPUs can be implemented as long as there is free space on the device. However, as I've said before, I recommend that you start with a single core and use the most orthodox method until you get used to all the hardware/software/tools. Even a single core can be used for a variety of purposes, but there are already many sample designs and examples that have been introduced, so I will refer to those and focus on multi-core this time.

Multi-core CPU configuration

Target type (load distribution type)

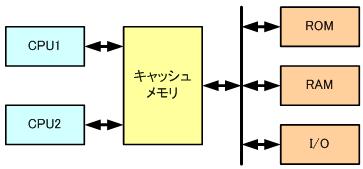

When you hear the term multi-core CPU, you probably think of the CPUs installed in recent personal computers. Figure 1 shows an example configuration of a dual-core CPU. This is commonly called a target type, and it is a mechanism for efficiently running multiple applications or one multithreaded application under the control of the OS (Operating System). No matter how many CPUs there are, they seem to operate like one CPU, so memory such as ROM/RAM and I/O are shared by all CPUs. Another feature is that there is no need to think about which CPU to run on when building software. It is especially effective in environments where multiple clients, such as servers, access it at the same time. I don't think this symmetric type is suitable for embedded use.

Figure 1 Symmetric configuration example (dual core)

非対称型(機能分散型)

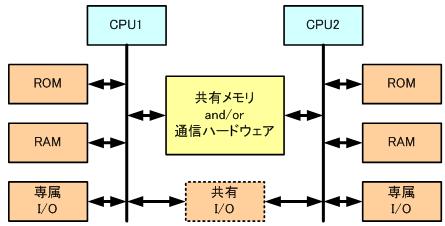

In contrast to the symmetric type, in which CPUs are allocated according to load at the time of software execution, the asymmetric type predetermines the processing content of each CPU at the system design stage. As shown in Figure 2, each CPU has its own memory and I/O to be controlled, and data exchange between CPUs is loosely coupled using shared memory or serial/parallel communication. Some applications may have shared I/O. Also, since functions are assigned to each CPU, the most important feature is that the optimum CPU and operating speed can be selected for each function. Mobile phones and car navigation systems are equipped with a large number of functions such as communication, image/audio processing, file processing, etc., and centralized processing with a single CPU (including symmetric type) is not realistic from various points of view. . This asymmetric type is suitable for embedded devices.

Fig. 2 Configuration example of asymmetric type

Soft-core CPUs can be freely configured by the user, so they can be configured as either symmetric or asymmetric types, but symmetric types cannot compete with existing CPUs in cost performance, and I don't think vendors are targeting them. Therefore, we will talk about the asymmetric type, but since the general configuration is shown in Fig. 2, we will explain a little more in-depth use case. For the sake of explanation, we will use the functional distribution type expression instead of the asymmetric type.