hello.

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

This time, Intel Quartus ® Efficient pin layout design with Prime Pro Edition development software interface planner” will be introduced.

Target environment

|

Eligible Quartus Prime |

Quartus Prime Pro Edition |

| Target FPGA | FPGA families supported by the version of Quartus Prime Pro Edition you are using |

Challenges in I/O planning

The main challenges in making I/O assignments in modern FPGAs are:

・ Increasing complexity of I/O standards and FPGA I/O structure

⇒ More guideline steps required for accurate pin placement of designs

・PCB development at the same time (or slightly earlier) than FPGA design

・Verify pin assignments early in the design cycle

Quartus Prime has the following existing solutions to address these challenges:

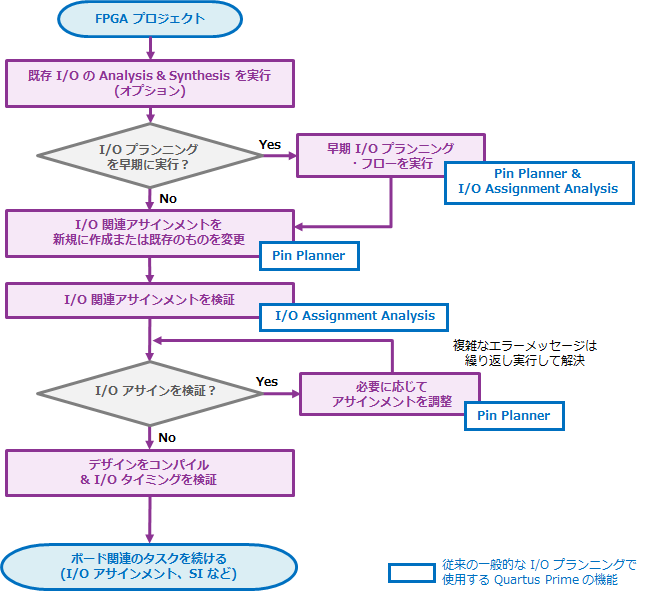

Until now, to create an I/O floorplan,

I think that Pin Planner and I/O Assignment Analysis were used respectively in the work flow of the figure below.

In this flow, I/O Assignment Analysis analyzes pin assignments.

The accuracy of I/O Assignment Analysis depends on the completeness of your design.

If any errors are detected, Pin Planner or other tools should fix the defects and run the I/O Assignment Analysis again.

This cycle continues until all I/O assignments are completed and verified.

Intel's FPGAs currently support a variety of protocols demanded by the market.

It also supports a large number of memory interfaces, each with their own placement rules.

The more interfaces you have in your design, the more complicated the rules and restrictions will be.

Even if you think you've placed your design interface correctly, you won't know if it's true until you run the Fitter or run I/O Assignment Analysis during full compilation.

If an element's placement is in an invalid position, resulting in a non-conformance, the long hours spent on a full compilation are wasted.

interface planner

The Quartus Prime Pro Edition Interface Planner is a pin layout tool that allows you to graphically create and validate complex I/O interface assignments in real time according to pin placement rules.

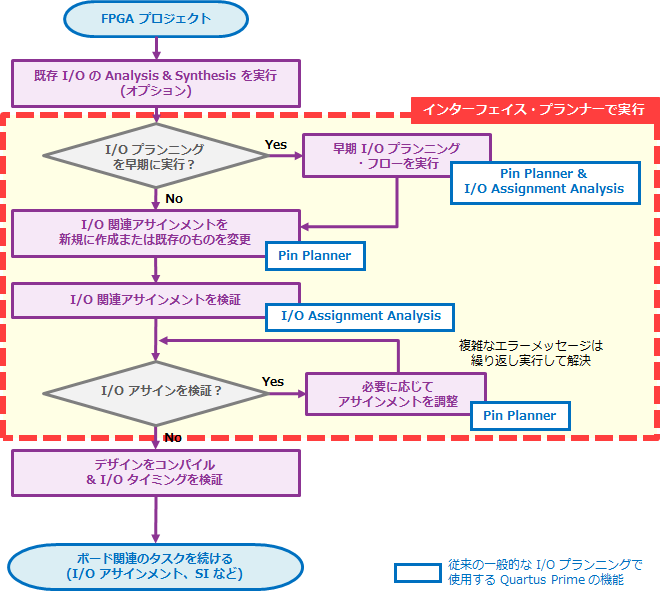

The figure below shows the work flow for I/O floorplanning with the interface planner.

The interface planner uses the Fitter to verify pin assignments in real time. Therefore, we perform logic synthesis (Synthesis) in advance, but the design does not have to be complete.

Simply drag and drop or double-click onto the floorplan to assign the interface design to the device's resources.

The created assignment plan is generated and executed as a TCL script, and compiled after reflecting the project.

work outline

The interface planner work flow is as follows: It is assumed that pin assignments by the user have been completed.

- Synthesize the design

- Start/Initialize Interface Planner

- Check imported assignments and update plans

- Place design elements

- Validate I/O plan

- Export plan file

- Import into project and compile

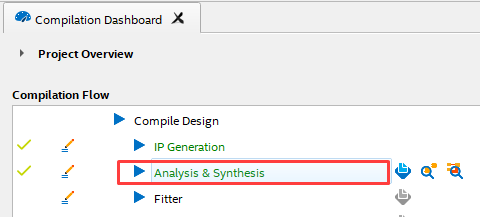

1. Synthesize the design

Execute Analysis & Synthesis from the Processing menu or Compilation Dashboard in Quartus Prime Pro Edition (hereafter referred to as Quartus Prime).

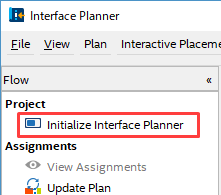

2. Start and initialize interface planner

Launch Tools menu > Interface Planner.

Click Initialize Interface Planner in the Flow pane to check Fitter-based validity and existing location assignments.

If there are conflicts or violations, error messages are displayed in the Console pane.

3. Check imported assignments and update plans

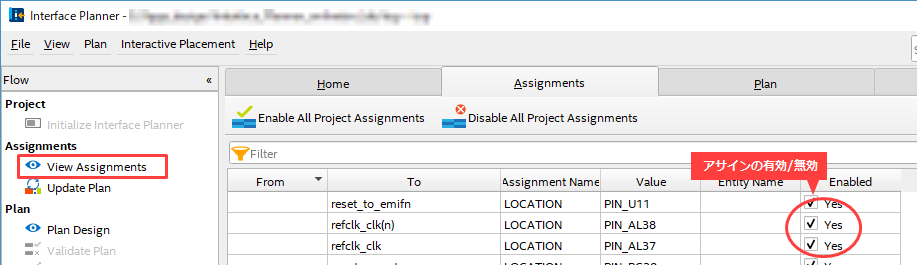

Click View Assignments in the Flow pane. (The Assignments tab becomes active.)

The Assignments tab becomes active, listing all assignments that exist in the project.

Click Update Plan in the Flow pane.

Enabled Assignments are applied to the design for rule checking.

4. Place design elements

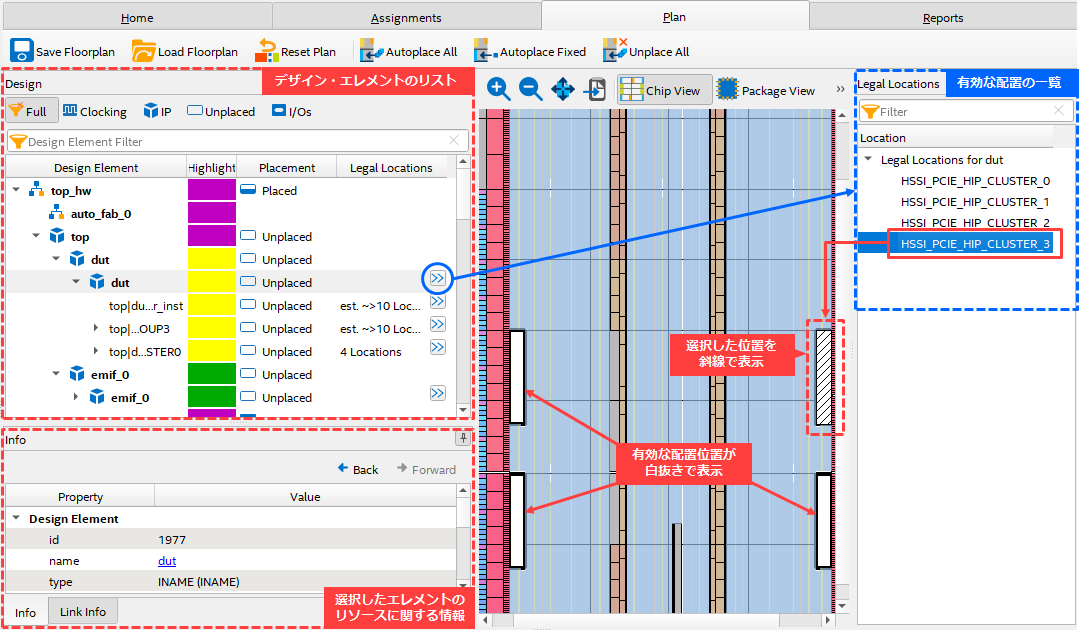

Click Plan Design in the Flow pane. (The Plan tab becomes active.)

Clicking the button to the right of an unassigned design element in the Design pane displays a list of assignable locations in the Legal Locations pane, and the locations are displayed in white in the Chip View.

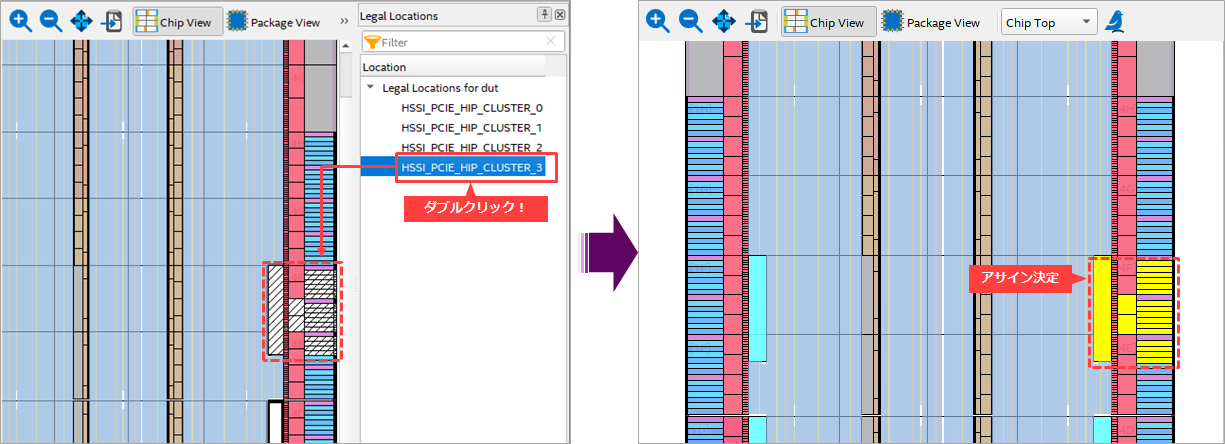

Specifying a placement location from the Legal Locations pane results in diagonal lines in Chip View.

Double-click the location in the Legal Locations pane to confirm the assigned location.

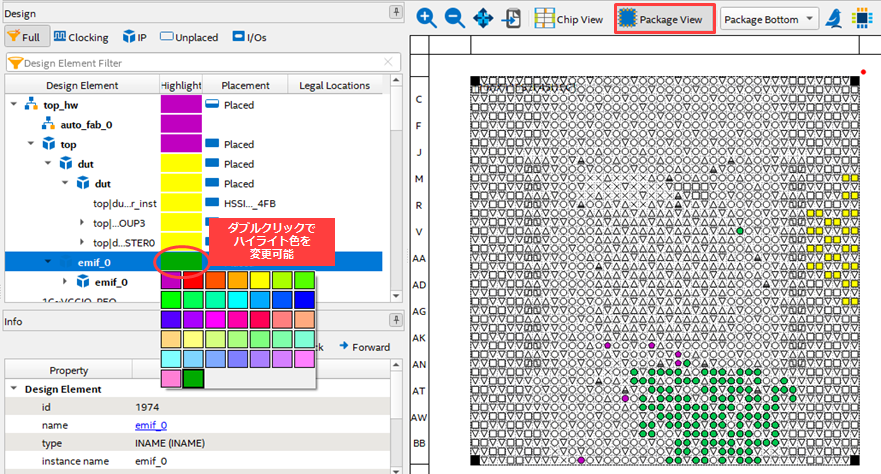

You can also switch to Package View to see the I/O pins used by the interface. You can also take a screenshot of your plan for later comparison with your compiled design.

5. Validate the I/O plan

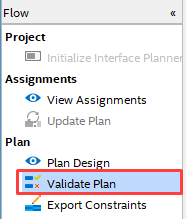

After completing the deployment specification, click Validate Plan in the Flow pane.

This validates the assignment you created and prepares it for export.

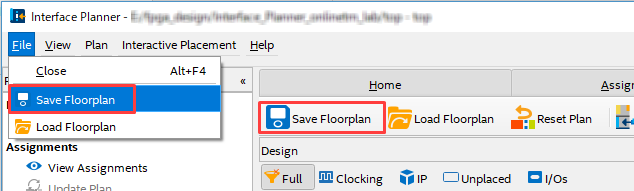

You can also select Save Floorplan to save the current layout settings.

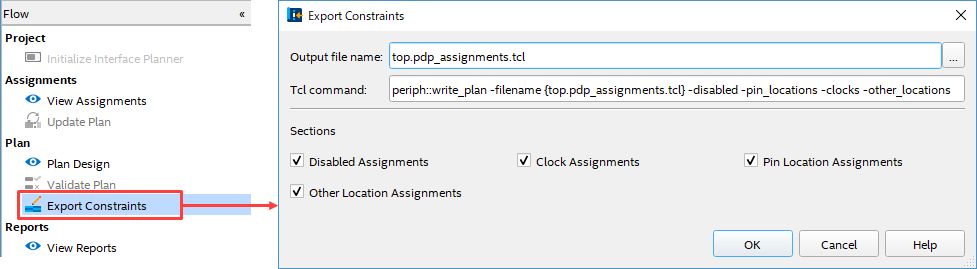

6. Export plan file

Click Export Constraints in the Flow pane to save the placement information you have set as a tcl script.

7. Import into project and compile

Close the Interface Planner and open the destination Quartus Prime project.

From Tools menu > Tcl Script, specify the exported tcl file and click Run to apply it.

Assignment information is reflected in the Pin Planner and Assignment Editor, making it easy to see and finalize the script information.

It is also possible to edit the script with the Edit button before executing the Run.

For example, without reflecting in the design all types of assignments exported by the interface planner. If you only want to make pinout assignments and not internal resource assignments, you can provide just the pinout assignments section of the script by commenting it out or removing it.

Then run the compile.

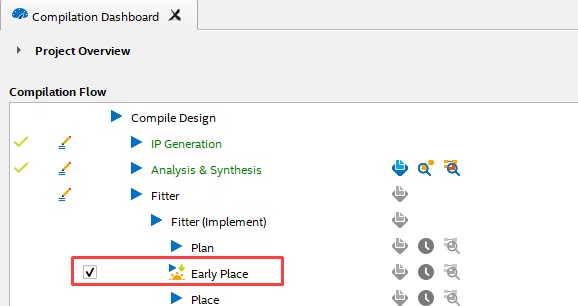

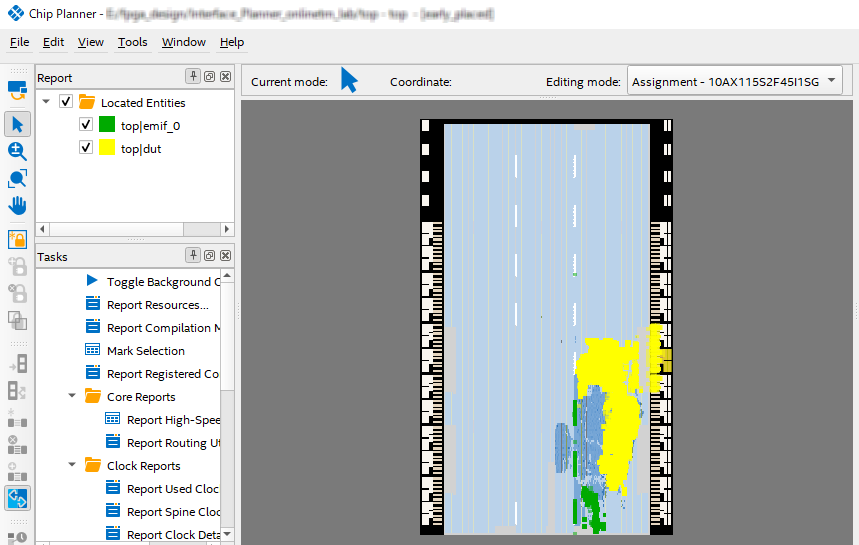

Since the execution from Analysis & Synthesis to the Fitter (Finalize) stage takes a long time, if you just want to evaluate the placement, you can enable the Early Place option in the Compile Dashboard and perform an Early Place compilation.

After compilation, launch the Chip Planner (Tools menu) to check the placement.

Summary

Quartus Prime Pro Edition's interface planner saves the trouble and difficulty of creating professional plans for FPGAs with increasingly diverse and complex I/O interfaces, and can create only valid location assignments. is.

You can reduce the amount of time you spend on location assignments by using the interface planner.