Hello. My name is Taro Washimiya and I provide technical support for Intel® FPGA products at Macnica.

This time, we will talk about a new interface standard that connects FPGAs and next-generation CMOS image sensors. These days, I feel that the number of development projects using image sensors is increasing rapidly through daily business negotiations. The FPGAs I am in charge of are often used to connect with image sensors, so I am always interested in applications and related technologies.

I recently learned about cutting-edge interfaces and their intellectual property (IP) at Macnica 's development department, and I would like to introduce them to you.

Introduction

Sony, which holds a large share of the CMOS image sensor market, has established the "SLVS-EC standard," a new interface suitable for next-generation high-resolution CMOS image sensors. The company is also vigorously promoting the commercialization of image sensors equipped with this interface.

Macnica was one of the first to notice this new interface, and developed the "SLVS-EC Rx IP" to easily connect to FPGAs, and has begun offering it to customers. It was demonstrated at Vision 2016, held in Germany last year.

なぜ今、新しいインタフェース?

現在、イメージ・センサのインタフェースは LVDS (Low Voltage Differential Signaling) と呼ばれる低振幅差動インタフェースが主流です。コモン・モード・ノイズに強く、低振幅で高速にデータ転送ができるため、広い用途で使われています。

ただ、ますます高速化や高解像度化が進むイメージ・センサでは、大量のイメージ・データをより高速に、より低消費電力でというニーズが増加しています。LVDS は差動信号ペア 1レーンで約 600 Mbit/sec で送れますが、FPGA との接続では、8、16、32レーン、いやそれ以上も、というセンサ・ニーズが出てきています。LVDS は広く使いこなされている技術ですが、接続には全レーン間のスキューを正確に抑え込まねばならず、レーン数が増えれば増えるほど基板設計が困難になっています。従って「基板設計をなんとかしたい」というニーズも強まる一方です。

ソニーの「SLVS-EC規格」って?

Scalable Low Voltage Signaling Embedded Clock の略からのネーミングです。ネーミングから LVDS 同様の低振幅差動インタフェースで、高ノイズ耐性をそのまま受け継ぎ、更に低振幅・低電力で、クロック埋め込み型であることが大きなアドバンテージということです。

LVDS では、クロックがデータとは別のレーンで送る仕様のため、前出の基板設計が困難になるという問題が顕在化していますが、SLVS-EC ではイメージ・センサ側(送信側)でクロックをデータに重畳して送り、FPGA 側(受信側)でクロックを再生する方式のため、基板設計が容易になり、より高速に、より遠くまでデータを送ることができます。

更にソニーは、イメージ・センサに適用するインタフェースとして、上記「物理層」での特徴に加えて、初期化やモード変更など「リンク層」を定義・規格化していますので、ユーザにとってより使い易いインタフェースになっています。

「SLVS-EC Rx IP」で簡単接続!

Since this is a standard that includes the link layer, it is even easier to use if the dedicated interface circuit is IP. If you use the "SLVS-EC Rx IP" developed by Macnica for receiving, you can easily connect the SLVS-EC interface even if you don't know much about the standard.

Here we will show the features and outline specifications of the SLVS-EC Rx IP.

Features

- SLVS-EC Specification Version 1.2 対応

- SLVS-EC Link 層で定義される各種機能を実現(物理層は Altera PCS/PMA で実現)

- 各種レーン構成に於ける Byte to Pixel 変換をサポート

- ヘッダ解析とペイロード・エラー検出機能を搭載

Outline specifications

| function | 諸 元 |

| Transfer Rate | 2.3 Gbps/Lane |

| Clock | Embedded Clock (8b/10b Encoding) |

| Number of Lanes | 1, 2, 4, 6, 8 |

| Baud Grade | 1, 2 |

| Bit per pixel | 8, 10, 12, 14 |

| CRC | Limited* |

| ECC | Supported |

| Embedded data | Supported |

| Dynamic Mode Change | Supported |

| Multiple streams | Optional |

※使用する FPGA や構成により動作周波数を満たせない場合あり

デモンストレーションはどんなもの?

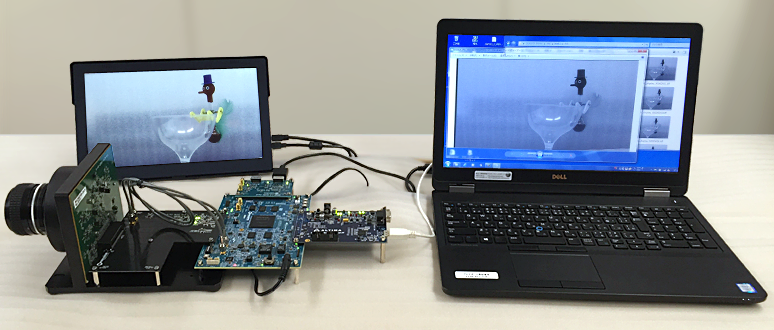

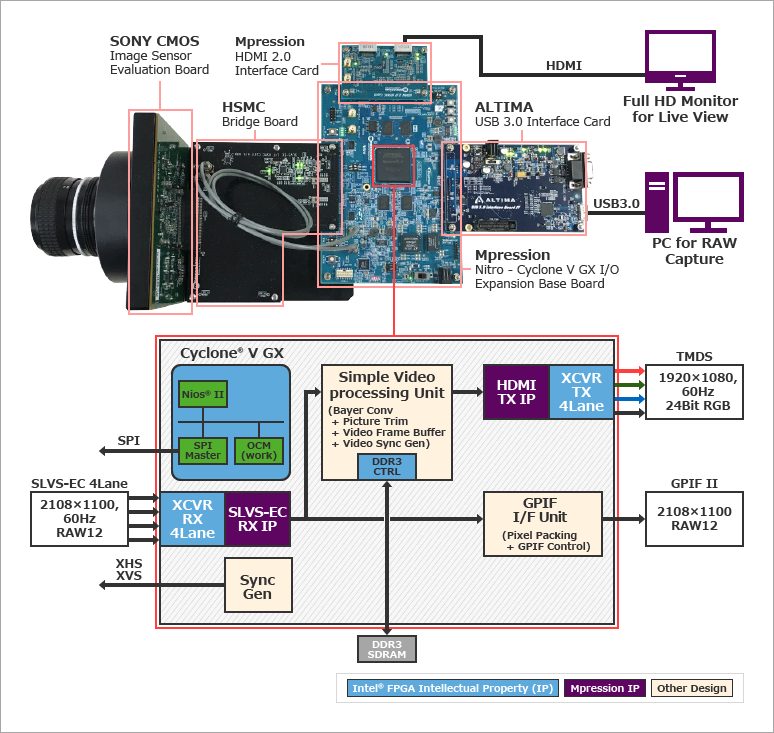

After all, there is a big difference in impressions when you see something new in action and when you don't. The demo they showed us this time was realized by using Sony's CMOS image sensor evaluation board and combining Macnica 's assets.

The image data received by the image sensor is transferred to the FPGA development kit "Nitro" via a 4-lane SLVS-EC interface, and then distributed within the FPGA to two output paths, one to the HD monitor via the HDMI interface. One displays live video, and the other outputs RAW image data to a PC via the USB3.0 interface. Of course, we can see that the SLVS-EC interface is working properly. It's difficult to understand in words, so I'll show you the connections using photos and a block diagram to help you understand the processing flow of the demo.

Unfortunately, this demo set is not on sale, but Macnica sells the "SLVS-EC Rx IP" as well as the IP and boards used in this demo separately, so you should be able to easily build a similar environment. think. Of course, the most important part, the imager, will need to be handled by Sony...

This is Taro Washimiya's latest technology report.

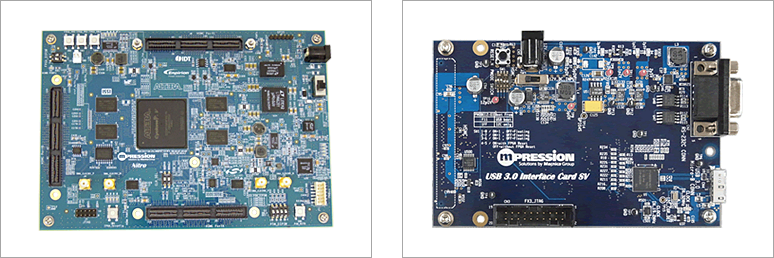

IP and boards available from Macnica

SLVS-EC Rx IP

HDMI 2.0 Tx IP

Nitro Cyclone V GX I/O 拡張ベースボード ALTNITROC5GX

USB 3.0 インタフェース・ボード ALTHSMCUSB3SV

紹介した IP やボード製品に興味がある方は、下記へご連絡ください。

Click here to purchase products

Nitro Cyclone V GX I/O 拡張ベースボード ALTNITROC5GX

USB 3.0 インタフェース・ボード ALTHSMCUSB3SV