Before compiling in FPGA development, it is important to check whether the created logic circuit (design) operates as expected.

It's important.

Today, hardware language (HDL) is the mainstream of design, and logic simulation is also done in language.

Input pattern information is indispensable for simulation, and the input pattern is also described by the designer in HDL, which is called a "testbench".

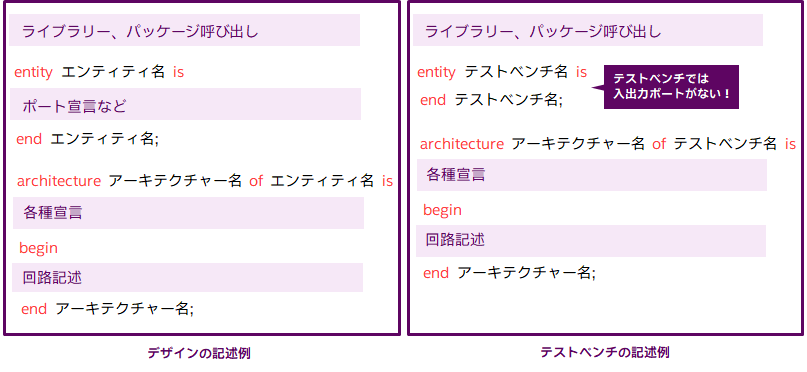

Here is a very basic description of a testbench.

VHDL の書式

When creating a testbench, call the package and describe the entity part (entity~) and the architecture part (architecture~) in the same way as when creating an FPGA design. However, since there are generally no input/output ports in the testbench, there is no need to write port declarations in the entity section. Therefore, the input conditions of signals to be input to the design to be verified are described in HDL in various declarations and the circuit description section.

Various declarations (component declarations & signal declarations)

"Various declarations" can be divided into "component declarations" and "signal declarations".

When writing a description that calls a lower layer design in the "circuit description section", declare the component of the lower layer design in the upper layer architecture section. It is easier to understand if the component name in the component declaration is the same as the entity name in the lower hierarchy.

Write all port names of the lower hierarchical design in parentheses after port. The input/output direction and data type are described in the port description, but unless these are the same as the entity part of the lower hierarchical design, the simulation cannot be performed correctly.

example)

component top_tb

port (

clock : in std_logic;

resetn : in std_logic;

test : in std_logic;

datain : in std_logic_vector (7 downto 0);

dataout : out std_logic_vector (7 downto 0)

);

end component;

Declaring Signals declares the signals used in the entity part.

Input signals to the design under test (mainly at the top level), output signals from the design under test, and signals used only within the testbench are described using the signal statement with signal names and data types.

example)

signal CLOCK : std_logic;

signal RESETn : std_logic;

signal TEST : std_logic;

signal DATAIN : std_logic_vector (7 downto 0);

signal DATAOUT : std_logic_vector (7 downto 0);

Circuit description part (lower hierarchy call & input condition description)

"Callingthe lower level (design under test)" is the same as calling the normal lower level.

Instance name: entity name

port map (

lower layer port name => current layer signal name,

lower layer port name => current layer signal name,

Lower layer port name => Current layer signal name

);

The following is a description example when the instance name is "u1" and the entity name of the design to be verified is "top".

example)

u1 : top

port map (

clock => CLOCK,

resetn => RESETn,

test => TEST,

datain => DATAIN,

dataout => DATAOUT

);

Description of input conditions to the lower hierarchy (verified design)

here mainly

- 常にレベルが固定している信号の記述

- 一定間隔で値がインクリメントする信号の記述

- Description of a signal that repeats '1' (high level) and '0' (low level) periodically or irregularly

This section explains.

Once you've mastered these, you'll be able to write your own testbenches.

Note that there are other description methods other than those introduced here, so please study and master them later.

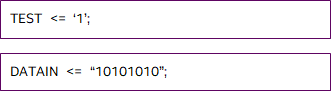

1. 常にレベルが固定している信号の記述

It can be written in one line.

When entering a numerical value, enclose it with ' ' (single quotation) for a single bit, and enclose it with " " (double quotation) for multiple bits.

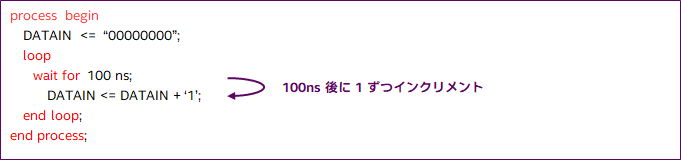

2. 一定間隔で値がインクリメントする信号の記述

Write the initial value after process begin.

Then use the loop statement to write an expression that increments at regular intervals.

When entering a numerical value, enclose it with ' ' for a single bit, and enclose it with " " for multiple bits.

3. Description of a signal that repeats '1' (high level) and '0' (low level) periodically or irregularly

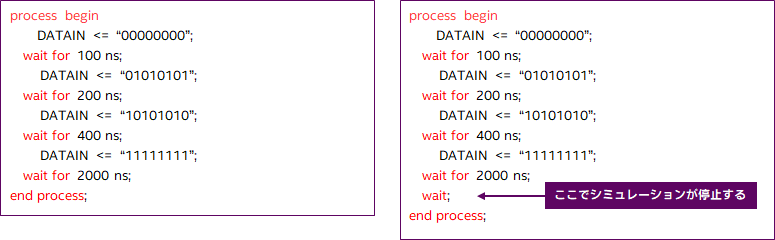

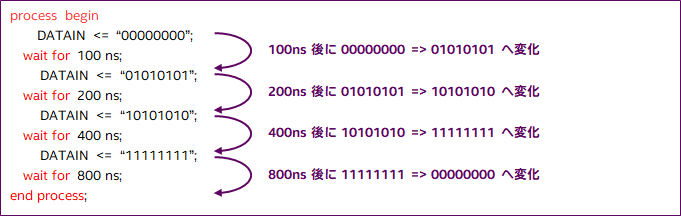

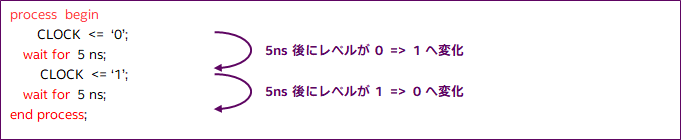

Describe the initial value after process begin, then describe the time until the next value change after wait for.

When entering a numerical value, enclose it with ' ' for a single bit, and enclose it with " " for multiple bits.

In this description, after executing to the bottom, exit the process statement, return to the beginning, execute, and repeat.

In our clock example, this description repeats '0' (low level) and '1' (high level) every 5 ns forever.

In other words, one cycle is a clock signal of 10ns (100MHz).

sample design

You can download the exercise data from the following page.

This sample also uses the description of the testbench, so please refer to it.

Coffee break: sensitivity list

A sensitivity list is a signal written in ( ) immediately after a VHDL process statement. When this signal changes, this process becomes active and the processing in begin to end process is executed. In the case of simulation, there are cases where this is not filled in. ( ) is also unnecessary when not describing the sensitivity list. It starts running when the simulation starts, and when it reaches the bottom it starts running again at the top, repeating forever.

コーヒー・ブレイク:シミュレーションの停止

VHDL does not have a dedicated statement to stop simulation. Therefore, the description using the process statement introduced earlier will not end forever unless the simulation is stopped by the simulator or the simulation time is specified and executed. Therefore, when you want to write a statement to the testbench to finish the simulation, use wait.

In the lower left example, after 100ns + 200ns + 400ns + 2000ns = 2,700 ns, exit the process statement, return to the beginning and repeat.

As shown in the lower right example, if you write wait before end process, the simulation will stop after 2,700ns.