Microchip FPGA: I want to use LVDS. What should I refer to for design creation and pin assignment?

For help creating the design, please refer to "UG0830 User Guide PolarFire FPGA Low Voltage Differential Signaling 7:1". https://ww1.microchip.com/downloads/aemdocuments/documents/fpga/ProductDocuments/UserGuides/microsemi_polarfire_fpga_low_voltage_differential_signaling_ug0830_v2.pdf

Regarding pin assignment

Please refer to the rules in "PolarFire FPGA and PolarFire SoC FPGA User I/O -Consolidated IOD Rules".

The IOD Rules can be downloaded as Consolidated_IOD_Rules_V1.xlsx from the link in Documentation > User Guides tab > PolarFire FPGA and PolarFire SoC FPGA User I/O -Consolidated IOD Rules.

https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas/polarfire-fpgas/polarfire-mid-range-fpgas#Documentation

Supplementary Note 1

Unlike GPIO, LVDS cannot be pin-freely arranged and wired. Please assign pins in advance.

Example error:

Error: PRPF-001: Port 'TXD[0]' for Interface 'LVDS_TX_0/PF_IOD_GENERIC_TX_C0_0' must be placed and locked before running Place and Route.

Supplementary Note 2

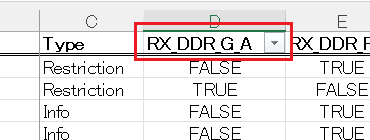

Please refer to the RX_DDR_x_x and TX_DDR_x_x listed on the first line of Consolidated_IOD_Rules_V1.xlsx according to the settings of PolarFire IOD Generic Receive Interfaces and PolarFire IOD Generic Transmit Interfaces.

Example: RX_DDR_G_A

The G in RX_DDR_G_A stands for global clock.

The A in RX_DDR_G_A stands for Aligned.

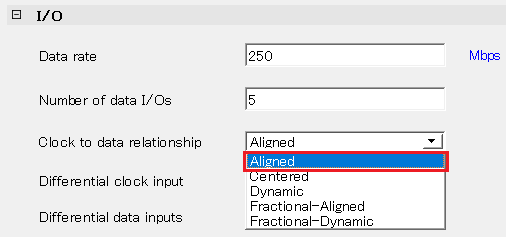

Similarly,

R is fabric regional clock

C is for Centered

DYN is Dynamic

FA stands for Fractional-Aligned

Refers to:

![]() Experienced FAE

Experienced FAE

Free consultation is available.

From specific product specifications to parts selection, the Company FAE will answer your technical concerns free of charge. Please feel free to contact us.