Introduction

In modern electronic equipment, accurate and efficient clock generation is a critical factor in system performance and reliability.

In this important role, Skyworks' clock products deserve special attention.

Skyworks' clock products have low jitter, flexible frequency customization, and support a variety of clock formats.

Suitable for use in communication systems and products that require precise data processing.

It can also provide economic benefits such as component consolidation, BOM cost reduction, and smaller mounting area, which is a big advantage for product designers.

In this article, we will explain how Skyworks clock products achieve these features and the three distinctive technologies behind them.

We hope you will learn about Skyworks' clock products, which are compatible with control devices such as FPGAs, SoCs, and CPUs, and can be safely used as peripheral devices, and consider them.

What are the three distinctive technologies of Skyworks clock products?

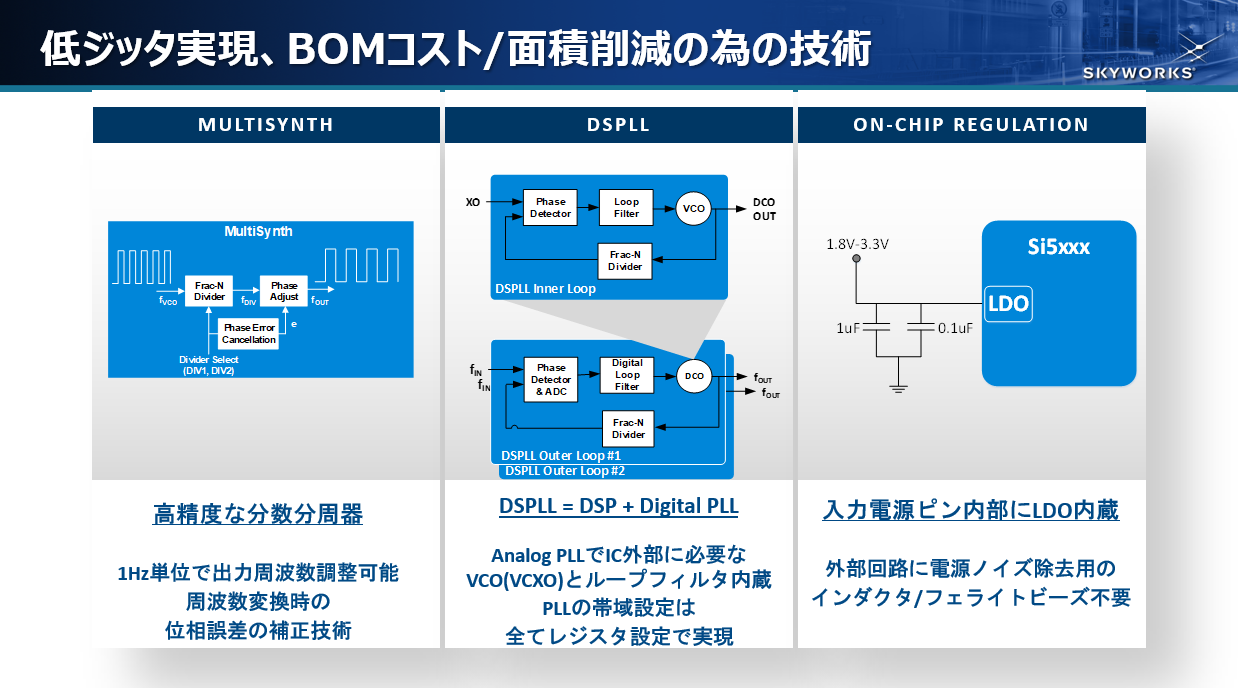

Skyworks has three unique technologies to achieve low jitter and reduce BOM cost/area: "MultiSynth", "DSPLL", and "On-Chip Regulation".

The diagram below provides an overview of the three technologies. I will explain each step in the next section.

MultiSynth technology

This is Skyworks' proprietary technology, and this MultiSynth technology allows for high-accuracy/high-resolution frequency settings. Specifically, it is an excellent technology that allows frequency setting in the 6th decimal place (1.000000MHz, or 1Hz increments) in the MHz order, and synchronized output with no phase error at 0ppm.

As a characteristic of general frequency dividers, jitter performance tends to deteriorate when dividing by Fractional compared to Integer, but MultiSynth has an internal function block that adjusts the phase shift when changing the frequency. It has the feature that jitter performance does not deteriorate significantly.

Clock generators such as the Si5391 and Si5332 are examples of devices that incorporate this technology.

Clock frequency example: Video signal 148.5MHz/1.001=148.351648MHz

Ethernet 161.132812MHz etc.

The figure below shows the block diagram of MultiSynth.

Click here for more information about MultiSynth

DSPLL

DSPLL is a word coined by Skyworks that combines DSP (Digital Signal Processor) and PLL.

One PLL has another built-in PLL nested inside it, which works to further reduce the jitter of the input signal.

It combines an analog LC-VCO with a DSP-based digital loop filter and digital phase detector.

In this way, the VCO (VCXO) and loop filter that are required outside the IC of conventional analog PLLs are built into one DPLL, leading to a reduction in the number of components and mounting area.

In addition to jitter attenuation, some DSPLL-equipped devices also have arbitrary frequency conversion (FOTF), hitless switching, and holdover functions, and all PLL bandwidth settings can be achieved by register settings.

Examples of devices that incorporate this technology include Skyworks crystal oscillators (XO, VCXO) and jitter attenuators such as the Si5392/4/5 and Si5396/7.

Source: "Innovative DSPLL® and MultiSynth Clock Architecture" (p.4: Figure 2. Skyworks' Fourth-Generation DSPLL Architecture vs. Traditional Approach)

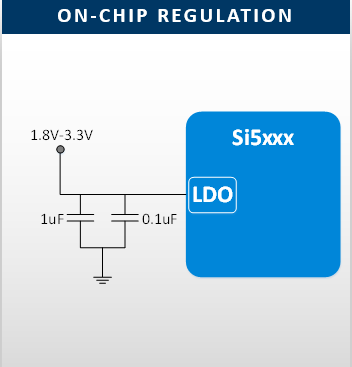

On-Chip Regulation

Part numbers starting with Si5xxx have an integrated LDO inside the input power pin of the chip. The output driver side also has a built-in LDO for each output pin, which works to reduce crosstalk.

Additionally, as a noise countermeasure for the power line section, there is no need for inductors or ferrite beads to remove power supply noise in the external circuit, leading to a reduction in the number of components and mounting area.

Related Documents

Whitepaper

Contact Us

For inquiries regarding this product, please click the button below.

To Skyworks manufacturer information Top

If you want to return to Skyworks' manufacturer information top page, please click below.