Supports IP network transmission and time synchronization

Overview

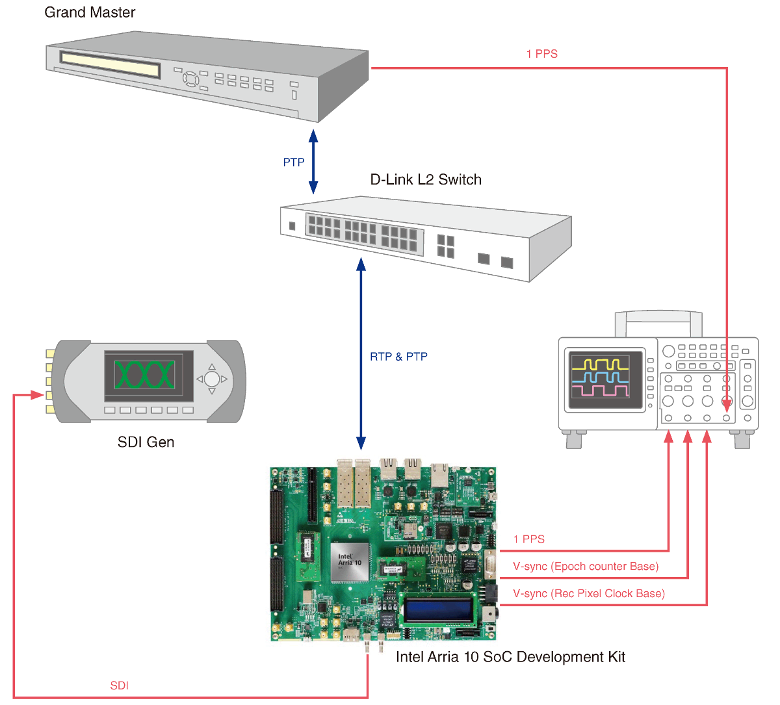

It uses IEEE 1588v2 Precision Time Protocol (PTP) to generate timing signals defined by SMPTE® ST2059, which can be used as GenLock signals traditionally used in IP-based A/V transmission.

Features

- Supports IEEE 1588v2 Master/Slave mode

- Can be customized more flexibly by combining with FPGA HW

- Stronger Network Jitter Tolerance

- Shortened lock time

specification

- IPv4 Base

- Supports both Master/Slave

- Video/Audio AP output

- 1pps output

- TC output

corresponding device

- Cyclone V SX

- Arria 10SX

(*Please contact our sales department for the compatibility status of other devices.)

Offerings

- Binary SW

- Cryptographic RTL (Verilog HDL)

- Reference design

- Various manuals

logic resource

Please contact our sales department.

demo image