Equivalent to Yaskawa JL-100/JL-102 dedicated LSI

Overview

The MECHATROLINK-III Master/Slave IP is regulated by the MECHATROLINK Association depending on the combination with the CPU.

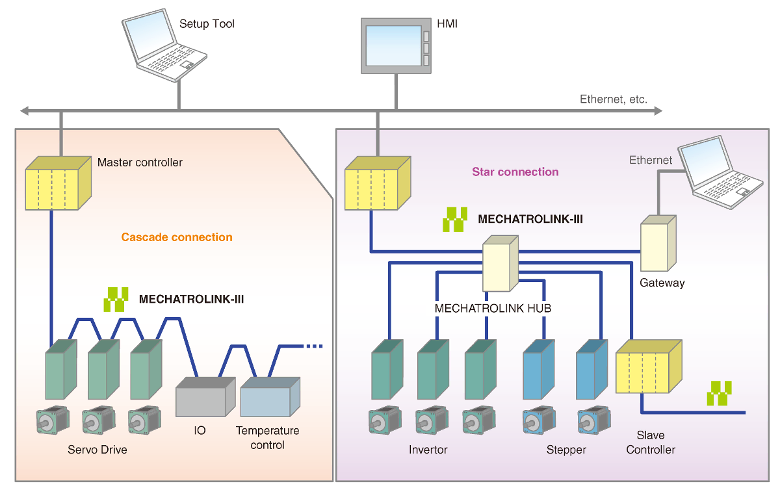

An IP that enables communication with MECHATROLINK-III compatible products.

Features

- Functionally compatible with the JL-100 communication ASIC with built-in MECHATROLINK-III master/slave communication functions

- Supports the functions required for MECHATROLINK-Ⅲ communication by setting from the external terminal and CPU

- Certified by the MECHATLOLINK Association

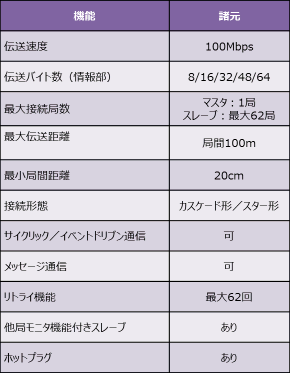

specification

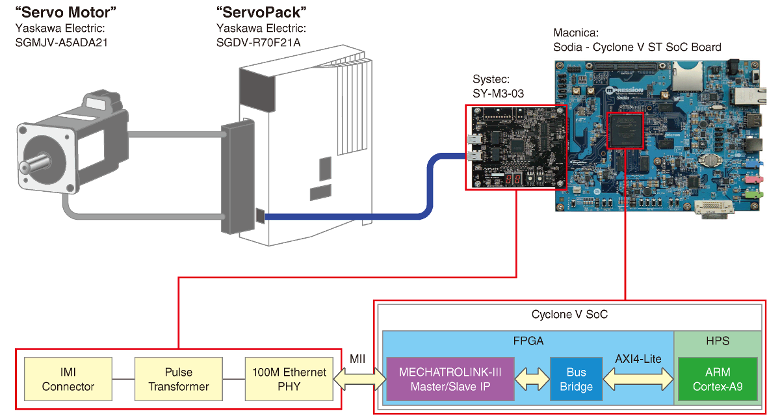

corresponding device

- Intel Cyclone® V

- Texas Instruments Sitara™ (supports single slave function only)

(*Please contact our sales department for the compatibility status of other devices.)

Offerings

- IP(暗号化ネットリスト)

- Reference design

- User's Manual

logic resource

*The above values are approximate circuit scale values based on implementation examples. It may vary depending on the customer's system configuration.

System configuration example

confirmation demo