Achieves high-speed serial transmission using V-by-One® HS standard

Overview

V-by-One® HS Tx/Rx IP is an IP for realizing V-by-One HS high-speed interface.

V-by-One® HS is a next-generation high-speed interface standard proposed by THine Electronics for imaging and video equipment.

By implementing Mpression's V-by-One® HS Tx/Rx IP in Intel® FPGA, the number of signals can be reduced compared to conventional LVDS interfaces, leading to significant reductions in product costs.

Features

- Achieves a maximum transmission bandwidth of 4 Gbps per lane (depending on the FPGA used)

- Supports not only video formats regulated by VESA/SMPTE, etc., but also user-customized video formats

- Flexible multi-lane design is possible according to customer's transmission band

- Equipped with a self-check function (FieldBET function) for checking communication between sending and receiving IPs

specification

| Transmitter IP (TX) | Receiver IP (RX) | |

| LANE | 1-32 | |

| Pixel Data | 24, 32, 40 bits | |

| Seif Test Function | FieldBET Pattern Generator | FieldBET Pattem Checker |

corresponding device

- Altera® Agilex™ 5E (Group B)

- Altera® Agilex™ 7(F Tile)

- Altera® Stratix® 10 GX (H/L Tile)

- Altera® Arria® 10 GX

- Altera® Cyclone® 10 GX

*Please contact us for information regarding the Altera Stratix® V GX, Arria® V GX, and Cyclone® V GX families.

Offerings

- Cryptographic RTL (Verilog HDL)

- Reference design

- Simulation environment (for Modelsim)

- User's Manual

- Reference Design User's Guide

Logic Resources (Altera® Arria® 10 GX)

RX

| 2Lane | 4Lane | 8Lane | 32Lane | |

| ALMs | 2,419 | 4,640 | 9,262 | 37,265 |

| registers | 4,977 | 9,956 | 19,914 | 79,309 |

TX

| 2Lane | 4Lane | 8Lane | 32Lane | |

| ALMs | 1,531 | 3,067 | 6,709 | 24,542 |

| registers | 2,814 | 5,567 | 11,276 | 45,076 |

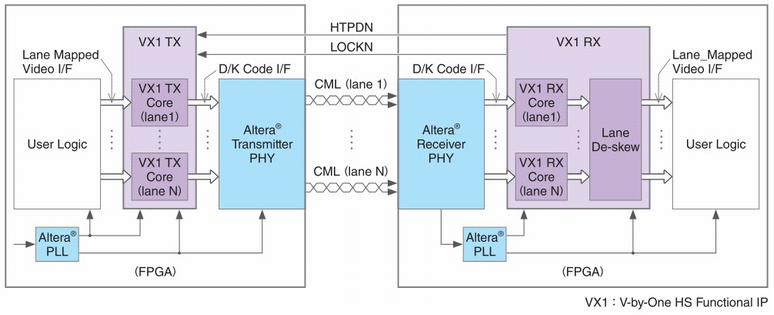

Diagram

Evaluation Board