Risk of "ringing", "overshoot" and "undershoot"

Engineers who design circuit boards may have had trouble with the "oscillator termination method."

This article provides a detailed explanation of how to terminate a single-ended oscillator.

For clock signals with abrupt rise and fall times, the traces on the printed circuit board (PCB) must be treated as transmission lines, not just wires. If the length of the trace exceeds a certain limit, the impedance of the trace must match the impedance of the source or load. Impedance mismatch can cause signal reflections on the transmission line, resulting in signal distortions such as "ringing", "overshoot" and "undershoot".

Specific termination method guidelines and points

1. Lumped constant circuit and distributed constant circuit

Lumped constant circuits ensure that the clock source, PCB trace, and clock receiver respond at the same time.

In a distributed constant circuit, each response is transmitted along the trace with a delay.

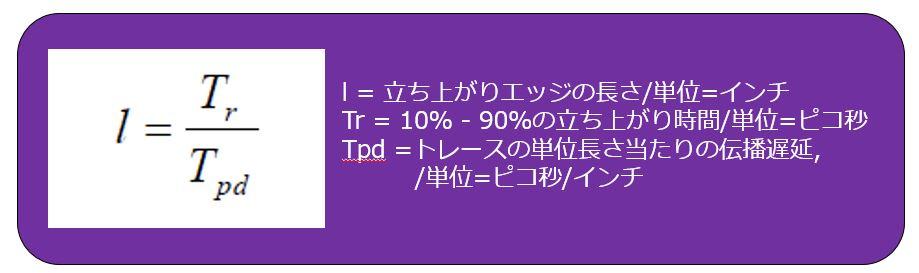

In fact, there is no such thing as a perfect lumped circuit because there is a delay when a signal propagates, but if the ratio of the effective length of the clock edge to the PCB trace length, as shown in Equation 1 below, is 1/6 or less, it can be considered as a lumped circuit (without having to consider termination).

For example, the propagation delay for FR-4 PCB traces ranges from 140 to 180 picoseconds per inch.

Assuming Tpd = 150 picoseconds/inch, the effective length of a 1 nanosecond rising edge is 6.7 inches.

So if the PCB trace length is less than 1.1 inches (1/6 of the effective rising edge length), the circuit can be considered roughly a lumped circuit. If you define Tr as 20% - 80%, change this ratio to 1/4.

The SiTime datasheet lists the rise/fall time of the output signal for each drive strength and load capacitance. When calculating the effective length of the rising edge with Equation 1, use the lowest load option (usually 5 pF) in the Tr value table listed in the datasheet of each product (because the load capacitance at the receiver end does not affect the rise/fall time at the clock source end).

When the clock driver sends a clock edge to the transmission line, the edge reaches the load after a certain time, but if the impedance of the load (𝑍𝐿) and the impedance of the transmission line (𝑍𝑂) are different, part of the signal is reflected from the load toward the source, degrading the signal quality. In addition, if there is an impedance mismatch at the source end, part of the reflected signal is further reflected toward the load, further degrading the signal quality.

The following sections will help you minimize reflections when driving single or multiple loads.

This section explains termination methods to improve signal integrity (SI: digital signal quality, transmission signal quality).

2. When there is only one device to be driven

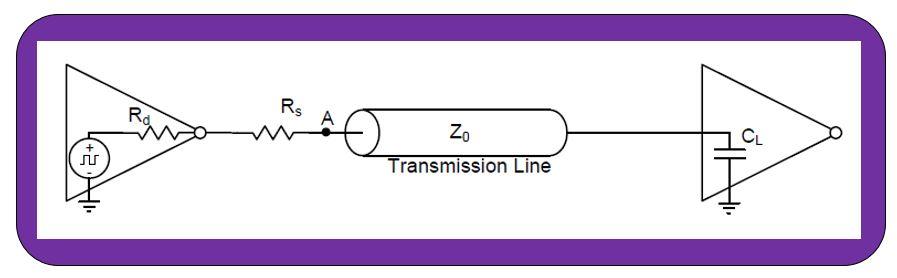

If you use series termination, place the resistor in series with the trace and as close to the source as possible(see diagram below).

To achieve impedance matching, the sum of the output impedance of the clock driver and the series termination resistormust be equal to the impedance of the trace.

Taking the SiT8208 as an example, the calculation method for the optimal termination resistor value is shown below.

Assumes an operating voltage of 3.3V and default drive strength driving 60Ω traces.

In the SiT8208 datasheet, the default drive strength setting code is specified as "F".

We can see that the output impedance that matches this suffix is 15.3 Ω.

Substituting this value into the equation, the source termination resistor value can be calculated as Rs = 60Ω - 15.3Ω = 44.7Ω.

Usually, the input impedance of the receiver is very large, about several megaohms.

At the receiver end, no energy may be absorbed and the entire signal may be reflected back towards the source.

Because the source and transmission line impedances are now matched, no further reflections occur.

We also recommend that you perform a layout simulation.

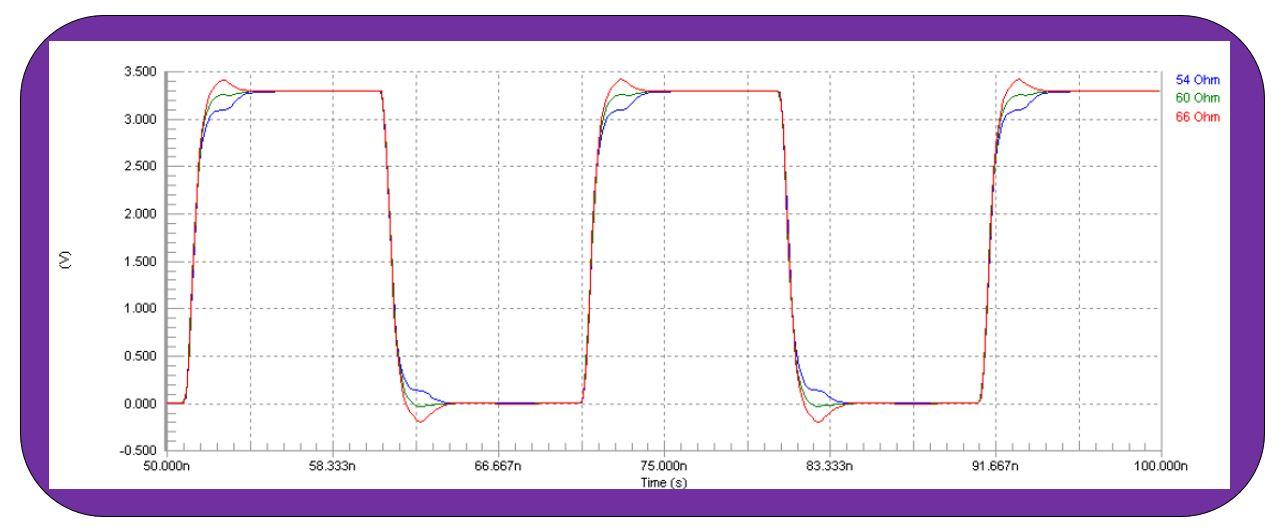

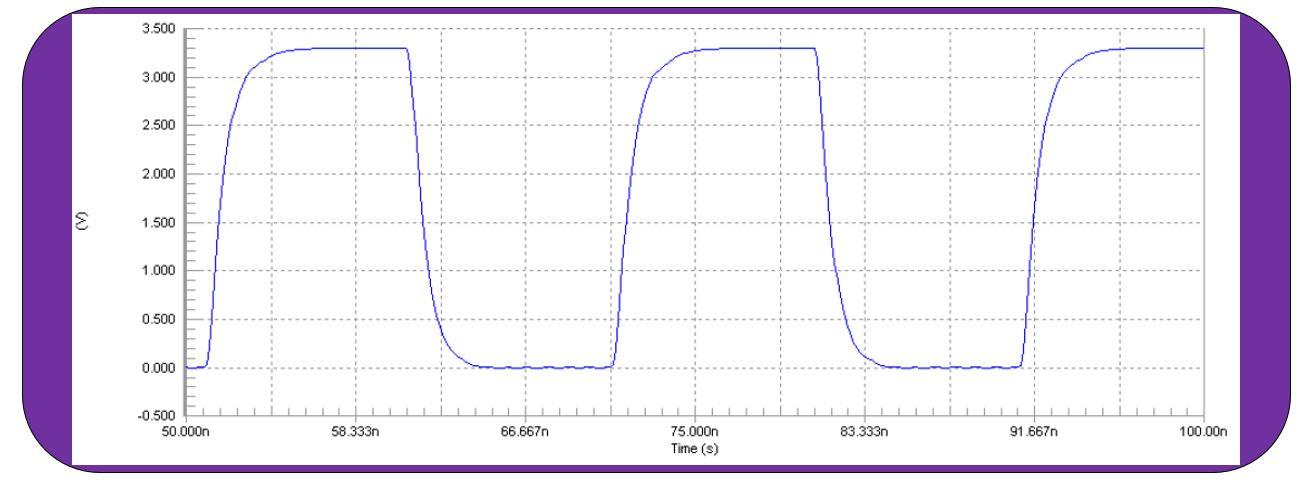

The signal waveform at the receiver end, assuming the SiT8208 is driving a 5 inch, 60 Ω transmission line, is shown in the figure below.

In this simulation, the termination resistor Rs is chosen to be 43 ohms to match the impedance of the 60 ohm transmission line. The figure also shows the results when the transmission line impedance varies by +/- 10% to account for variations in PCB manufacturing.

*Simulator: Altium Designer's Signal Integrity Analysis tool

3. When there are multiple devices to be driven

Besides ②, Multiple ICs on a PCB may require an input clock of the same frequency.

One approach to driving multiple loads with a single clock source is to use a clock buffer (a device with multiple clock outputs), but this requires additional board space and power.

An alternative is to drive multiple loads from one output terminal.

The key point is to drive multiple loads with one output terminal by designing the layout so that there is only one branch from the transmission line to multiple loads (= star connection) and keeping the trace length as short as possible.

This allows multiple loads to be represented as lumped constant circuits, which requires that the loads are placed close enough to each other (3-1).

If the distance between each load is long, it is necessary to consider a circuit model in which one output terminal drives two transmission lines rather than one transmission line (3-2).

The output driver will need to have a higher drive capability than just driving a single transmission line. It is also recommended that you perform signal integrity simulations using IBIS models before designing.

Some products may not have enough drive capability to drive two transmission lines, but if the spacing between the oscillator output terminals and the load is small enough, the system may be able to be represented in a star topology (3-3).

*SiTime output drivers are typically not capable of driving more than two transmission lines with an impedance of 50-60 Ohms, so we do not recommend driving more than two transmission lines with a single driver!

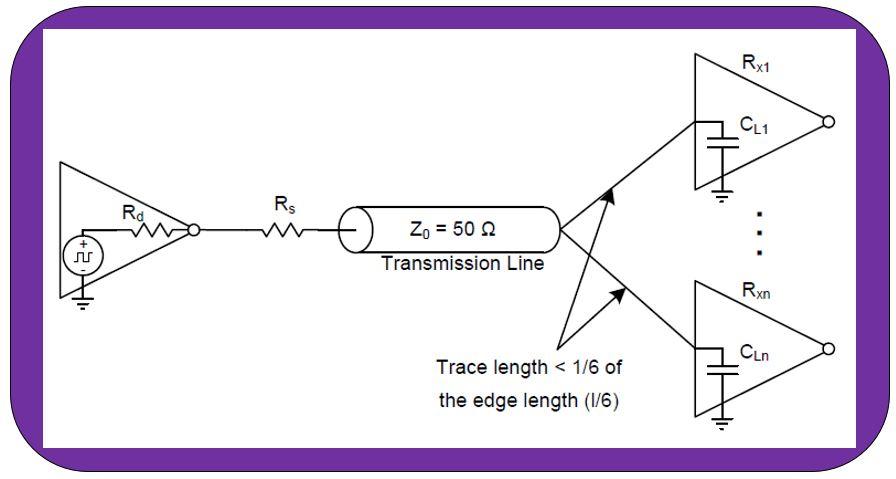

3-1. When driving multiple nearby loads

Having multiple loads in close proximity is simple.

If the effective length of the clock edge divided by 6 is shorter than the distance from the transmission line to each load, the system can be represented by this circuit model. The loads must be connected in a star topology as shown in the figure below. The series termination resistor value in this case can be calculated in the same way as for a single load.

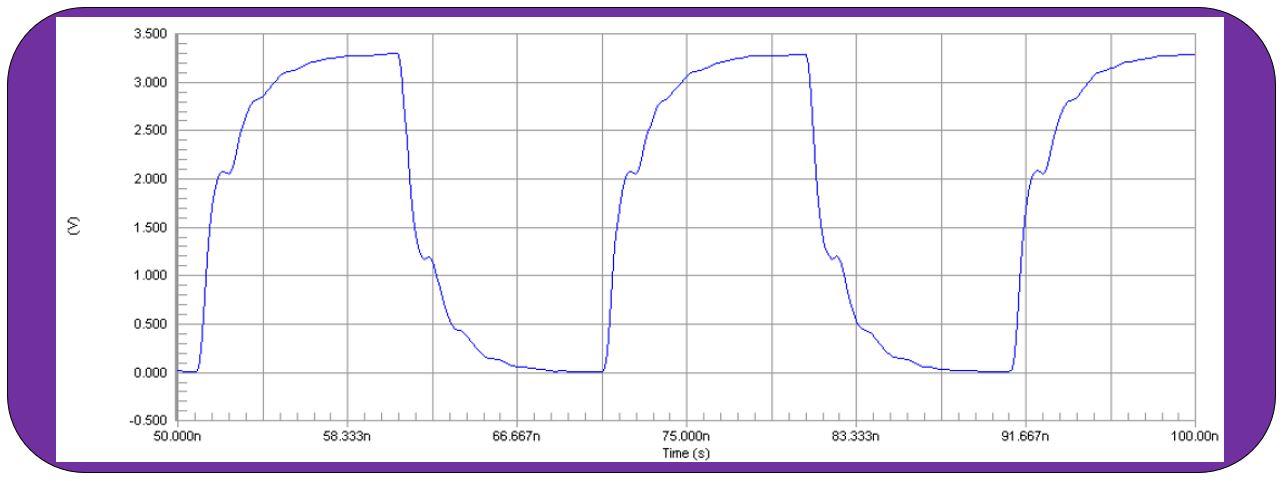

We also present the simulation results when this circuit is driven by a SiT8208 with a power supply voltage of 3.3V.

*Parameters: Rs = 43Ω, CL = 5pF, number of receivers = 2, distance from transmission line to receiver = 0.5 inches (~75 ps)

Simulation results also show that if the distance from the transmission line to the receiver is too long, reflections can cause signal integrity problems.

3-2. Driving two transmission lines from one source

In this case, the clock receivers are separated from each other. Since the load at the receiver end cannot be arranged as a lumped constant circuit, in this case, it is necessary to consider a circuit model in which the clock output terminal drives a separate transmission line for each load.

This method is low cost because it requires only one termination resistor per transmission line and provides full swing signal swing at the load, but for optimal signal integrity the following conditions must be met:

1. The clock driver must be able to supply sufficient peak current during the edge transmission.

2. All transmission lines are the same length

3. The load capacitance at the receiver end is approximately the same

4. The termination resistor is set to the value calculated below.

Rs = Z0 ー Rd ・N

Rs - Source termination resistor

Z0 - Impedance of the transmission line

Rd - Resistance of the driver output

N - Number of drive lines

3-3. Driving two loads in a star topology

If the source's driving capability is not strong enough to drive two transmission lines, a star topology can be considered.

In this topology, resistor Rt is used as the intermediate termination. The resistance of Rt is usually set to 1/3 of the impedance of the transmission line.

In a star topology, the termination resistor is usually placed at the load. In this case, the signal from the source driver passes through the intermediate termination without being reflected back at the branch point, and the signal that reaches the load is not reflected back to the source again by the load termination. This results in a good signal quality at the load without reflections, but with a very low amplitude that is not acceptable to many clock receivers. If there is no load termination and the load is high impedance, all the signal energy will be reflected back to the source. The impedance is matched at the midpoint by the Rt network, but the two reflected signals are combined here. In this case, it becomes very difficult to balance reflections and coupling to achieve acceptable signal integrity.

This star topology is not recommended if there is no load termination and the length of the transmission line is longer than one third of the effective length of the signal edge. For example, with an effective length of 1 ns signal edge, the length of the transmission line should not exceed 2 inches. Please feel free to contact us for simulation results.

in conclusion

We have explained the termination method using some simulation results.

If you have any questions, please feel free to contact us.

Inquiry / Sample Request / Quote

If you have any questions about SiTime products or would like to request samples, please contact us using the "Contact Us" button below.

If you would like a quote for a product, please request one by clicking the "Request a quote" button.