Let's consider the parameter change due to the temperature of SiC FET

Power transistors have several important parameters (FoM) such as drain-source resistance Rds and switching loss Eoss. These numbers are usually given in datasheets, but it is not always clear how these numbers change with temperature. These numbers are also affected by die area, resulting in FoM such as RdsA and Rds over area.

Of course, these numbers are "typical" and are generally given for an operating temperature of 25°C. These numbers are also derived from the Rds(on) at these "typical" conditions, showing how Rds(on) varies with temperature and, more importantly, its It doesn't take into account how the change varies by architecture.

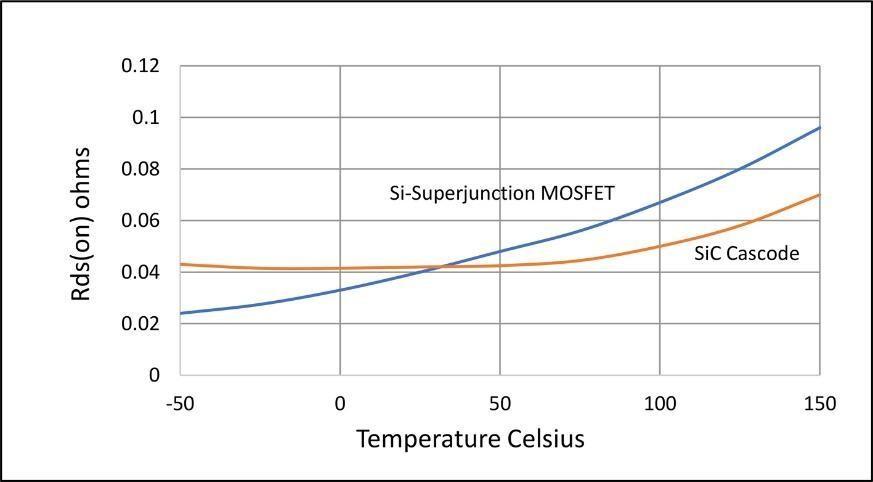

This can be clearly seen by looking at Qorvo's 650V SiC cascade device "UF3C065040K3S". The device has been documented to have an Rds(on) of up to 52mΩ (42mΩ typical) at 25°C. Comparing this to a 650V superjunction MOSFET with an Rds(on) of 45mΩ max (40mΩ typical), the superjunction device appears to perform better at this particular FoM. However, as Figure 1 shows, the situation changes dramatically when the temperature increases. Approaching 150°C, the Rds(on) of the superjunction device reaches 96mΩ, while the SiC cascade device remains at 78mΩ. In fact, even at 175°C, the Rds(on) of SiC devices remains at 78mΩ, which is significantly lower than the Rds(on) of superjunction devices.

It is clear from Figure 1 that the Rds(on) increase rate of SiC cascaded devices is much lower than that of superjunction MOSFETs.

Associated with this lower conduction loss, SiC cascade FETs consume less power at high temperatures, enabling power consumption as much as 30% lower than superjunction devices at 150°C. The amount of power dissipated also contributes to temperature rise, so less loss means cooler overall temperatures, and therefore even lower Rds(on) numbers. A lower Rds(on) also means more current can be carried, which is even more significant in the applications in which these devices are used. Another advantage of this FoM is that it minimizes die area, thus reducing switching losses and body diode losses.

The low rate of increase of Rds(on) with temperature for SiC cascade FETs is a feature of the high doping levels used in SiC. This moderates the decrease in electron mobility that increases with increasing temperature in all semiconductor materials. In addition, there are benefits in terms of gate charge and other FoMs, and engineers will find that using SiC cascaded FETs can lead to significant system-level design improvements and cost savings. .

Datasheets can show how a given device behaves under various conditions, but it is important to understand the effects of temperature and not to generalize between different types of devices.

Inquiry

If you have any questions regarding this article, please contact us below.

Qorvo manufacturer information top page

If you want to return to Qorvo manufacturer information top page, please click below.