Overview

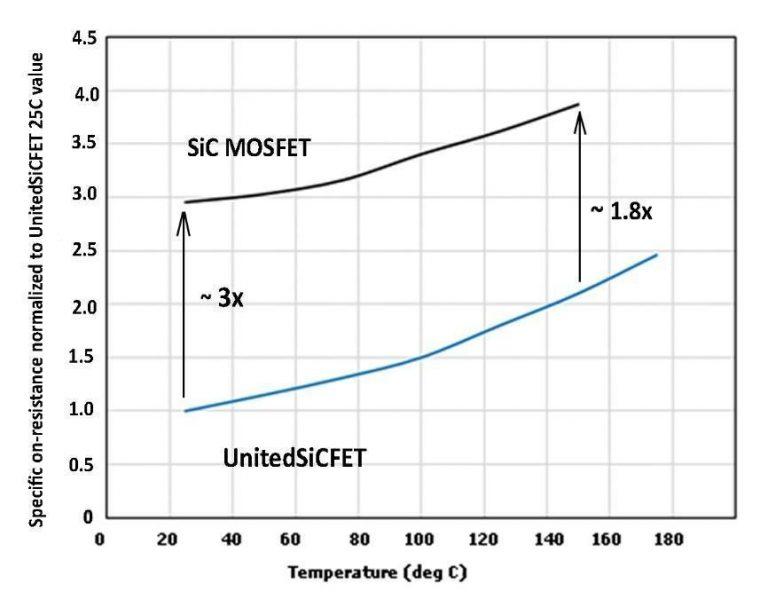

Comparing SiC switch datasheets can be difficult. SiC MOSFETs appear to have the advantage of a lower temperature coefficient of on-resistance, which indicates higher underlying losses and lower overall efficiency compared to Qorvo SiC FETs. A valid comparison requires comparing parts with the same voltage rating, the manufacturer's recommended gate drive voltage, the same junction temperature and drain current, and the same package.

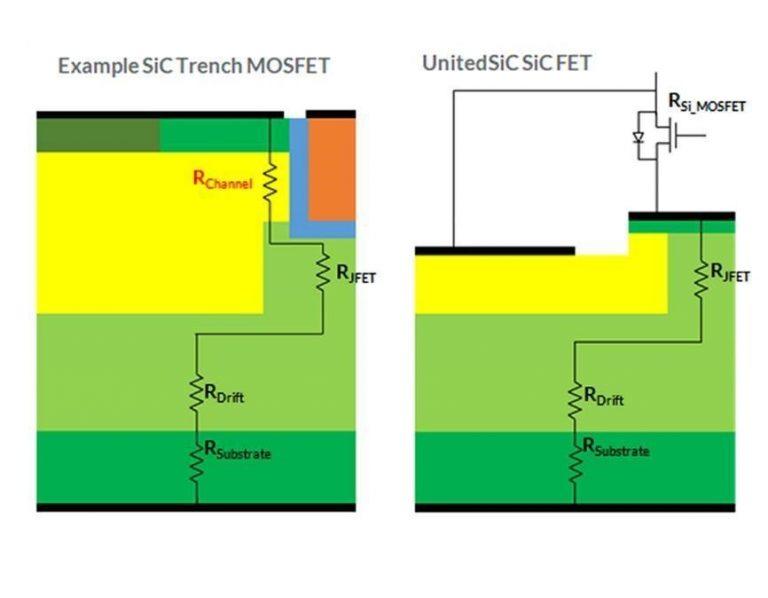

SiC MOSFET resistance is dominated by its channel resistance

The lower value of RDS(ON) temperature coefficient for SiC MOSFETs actually indicates a deeper effect. MOSFETs and JFETs are "single-carrier" devices with electrons flowing through different regions: the substrate, the drift layer, the JFET region, and the channel. In the 650VSiCMOSFET the inversion channel dominates the total resistance and actually decreases with temperature. Channel resistance is inversely proportional to (number of free carriers x mobility of electron inversion layer) and as temperature increases, threshold voltage decreases and the number of free carriers in the channel increases, thus decreasing resistance .

This effect is offset by the positive temperature coefficients of the rest of the device area, i.e. JFET, drift layer and substrate resistance, producing a small net positive Tc value. SiC JFETs do not have an inversion channel to offset the positive temperature coefficients of the JFET, drift layer and substrate. Low-voltage Si MOSFETs, on the other hand, account for only a small fraction of the total on-resistance, which explains their higher Tc values than SiC MOSFETs, but also the absence of losses associated with the non-ideal SiC inversion layer. can be seen (Fig. 1).

SiC FETs have low overall conduction losses

A look at the absolute values reveals something decisive. Comparing the RDS(ON) of the 650/750V devices, as shown in Figure 2, the Qorvo SiC FET starts with about one-third the specific on-resistance of the SiC MOSFET at 25°C and doubles at 150°C. A near improvement, with about half the conduction loss for the same active die area.

The net effect is that the healthy positive temperature coefficient of the Qorvo SiC FET and RDS(ON) results in lower overall conduction losses, ensuring effective current sharing between the cell and parallel devices. It is clearly beneficial to make sure the comparison is valid and to understand the mechanisms behind the effects. It can reveal what really matters: overall loss reduction.

Inquiry

If you have any questions regarding this article, please contact us below.

Qorvo manufacturer information top page

If you want to return to Qorvo manufacturer information top page, please click below.