本コラムでは、Ethernet MACとEthernet PHYをつなぐインターフェースについて説明していきます。

EthernetにおけるMII (Media Independent Interface)

EthernetのH/W構成

Ethernetにおける物理層は、伝送距離や通信速度によって同軸ケーブルやツイスト・ペア・ケーブル、光ファイバー・ケーブルなど、種々規定されています。これら物理的な接続仕様の違いを効率的に接続するため、物理層(レイヤー1(PHY))と論理層(レイヤー2(MAC))に分けられています。この物理層(レイヤー1)と論理層(レイヤー2)を接続する目的で定義された標準インターフェースがMIIです。

MII(Media Independent Interface)は10BASE規格のAUIに相当するもので、100Mbps Ethernetの「IEEE 802.3u」で定義されましたが、10Mbpsと100Mbpsに対応したMII、1000Mbps(1Gbps)に対応したGMII、10Gbpsに対応したXGMIIがあります。

次にMII、RMII、GMII、RGMII について簡単に説明していきます。

MII(Media Independent Interface)

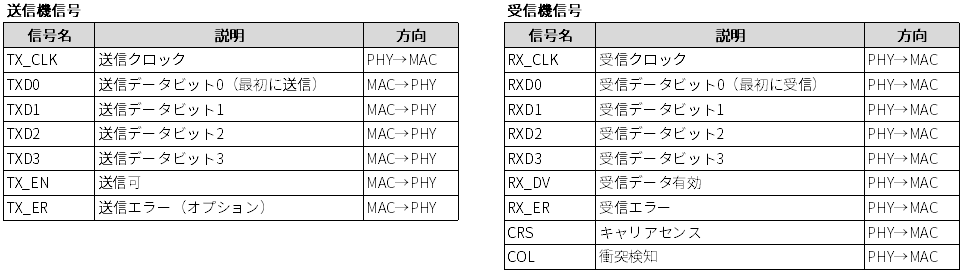

MII(Media Independent Interface)は、クロックと4ビット幅のデータ・バスが、送信用と受信用それぞれに用意され、リンク速度に基づいて100Mbpsの場合は25MHz、10Mbpsの場合は2.5MHzのクロックが、PHYによって生成されます。

25MHz(クロック周波数)×4bit(データパス)=100Mbpsを実現しています。

(2.5MHz(クロック周波数)×4bit(データパス)=10Mbps)

出典: フリー百科事典『ウィキペディア(Wikipedia)』

RMII(Reduced Media-Independent Interface)

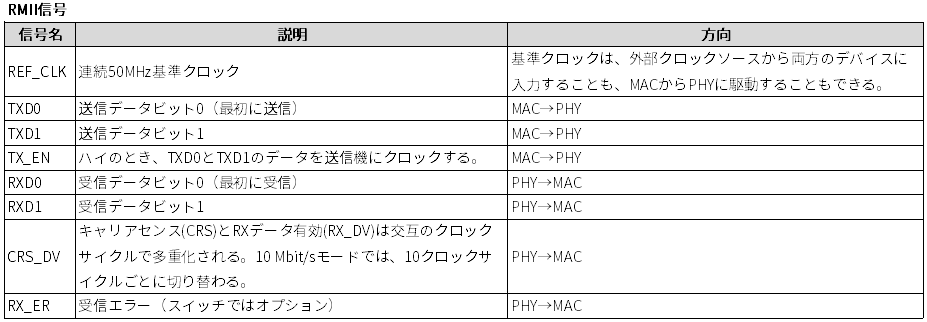

RMII(Reduced Media-Independent Interface)は、PHYとMACを接続する信号数を減らすために開発された規格です。50MHzのクロック(100Mbps/10Mbps 両方とも50MHzで動作します)と2ビット幅のデータ・バスで100Mbps通信を実現しています。

50MHz(クロック周波数)×2bit(データパス)=100Mbpsを実現しています。

出典: フリー百科事典『ウィキペディア(Wikipedia)』

GMII(Gigabit Media-Independent Interface)

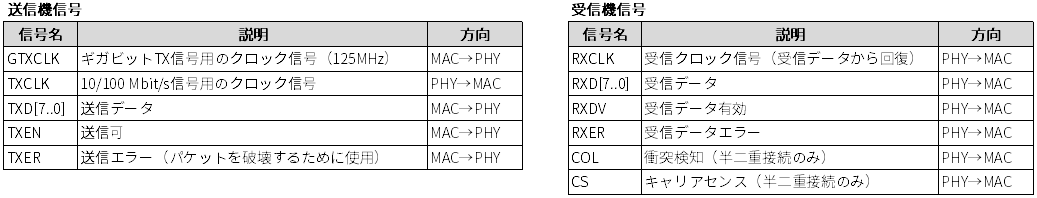

GMII(Gigabit Media-Independent Interface)は、125MHzのクロックと8ビット幅のデータ・バスが送信用と受信用それぞれに用意され、最大1000 Mbps通信を実現しています。

125MHz(クロック周波数)×8bit(データパス)=1000Mbpsを実現しています。

出典: フリー百科事典『ウィキペディア(Wikipedia)』

RGMII(Reduced Gigabit Media-Independent Interface)

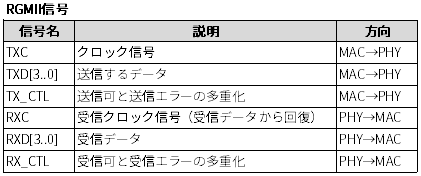

RGMII(Reduced Gigabit Media-Independent Interface)は、GMIIのデータ・バスを半分に減らしています。1000Mbpsでは、クロックの立ち上がりエッジと立ち下がりエッジの両方でデータが送信されます。10/100Mbpsでは、クロックの立ち上がりエッジでのみデータが送信されます。

125MHz(クロック周波数)×4bit(データパス)×2=1000Mbpsを実現しています。

出典: フリー百科事典『ウィキペディア(Wikipedia)』

SGMII(Serial Gigabit Media-Independent Interface)

Cisco Systems社によって規定されたSGMII(Serial Gigabit Media-Independent Interface)は、1000Mbpsを8B/10BエンコードでSerial転送する規格です。TX/RX Data 及び TX/RX Clockには、625MHzのクロック周波数のDDR差動ペアを使用しますが、TX Clockはオプション扱いとなっており通常は使用されません。その代わりに、RX Clockは差動ペアのデータからCDR(Clock and Data Recovery)により復元されます。データは、8B/10B Code-Groupsを使用してエンコードされます。(8B/10B Code-Groupsは、IEEE802.3 std. 36章参照)

一般的にGigabit Ethernetに使用されますが、10/100 Mbit/s Ethernetにも適用可能です。

625MHz(クロック周波数)×1bit(データパス(Serial転送))×2(DDR)=1250Mbpsを実現しています。

Microchip社 Ethernet関連製品情報

Microchip社のEthernet関連製品情報は、以下をクリックください。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

Microchip メーカー情報Topへ

Microchip メーカー情報Topページへ戻りたい方は、以下をクリックしてください。