I would like to introduce [soft error (SEU) resistance], which is a feature of Microchip's non-volatile FPGA, in three parts.

In the first installment, Microchip's non-volatile FPGA is "Why is it resistant to soft errors?" ] will be explained.

What is a soft error

Are you familiar with the term soft error?

Before the 1990s, there was a time when problems that occurred with extremely low regularity and reproducibility were regarded as "soft errors" and treated as problems with unknown causes.

In the 2000s, it became clear that the cause of soft errors was caused by neutrons. In recent years, the name SEU “S.E.U.” has become common. Soft errors and SEUs seem to be commonly used synonymously. Here, SEU is an abbreviation for Single Event Upset, and refers to defects caused by the influence of neutrons, and it can be said that defects caused by SEU are soft errors.

In recent years, we have heard that equipment problems caused by SEU require a large amount of man-hours for analysis and countermeasures. With the increasing use of SRAM-based FPGAs in mass production and SEU becoming a problem, the demand for Flash-based FPGAs that are extremely robust against SEUs is increasing.

Being strong against soft errors has the following advantages.

- Reduce man-hours for soft error analysis and countermeasures

- Improved reliability

From now on, I would like to introduce why Microchip's FPGA is strong against soft errors.

Comparison of FPGA configuration technologies

To begin with, PLDs are broadly categorized into the following technologies:

- antifuse

- UV erasable (EPROM)

- Electrically erasable ROM (EEPROM, Flash memory, etc.)

- Static memory (SRAM)

3 and 4 are programming technologies widely used in modern FPGAs.

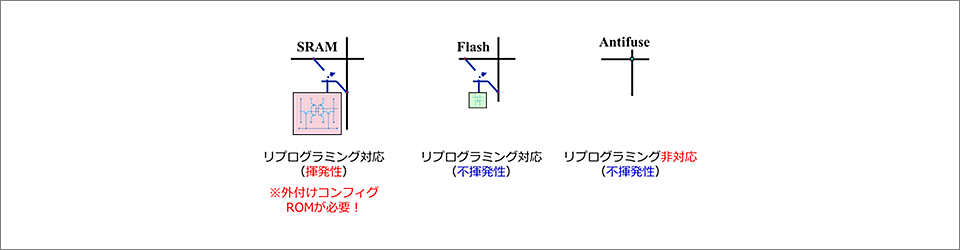

Next, a comparison of FPGA routing technologies is shown below.

SRAM becomes volatile and requires programming (downloading) from an external configuration ROM. Program the Flash cells directly, as the Flash will be non-volatile.

Antifuse, as the name suggests, connects by melting the contacts with a program.

Note) Fuses are blown (disconnected), but "anti" fuses are welded (connected).

SRAM is generally known to be greatly affected by SEU. On the other hand, Flash can greatly reduce the impact of SEU depending on the method and structure. As for Antifuse, it is unlikely that the SEU will generate enough energy to melt the contact, so it will not be affected. From the above, from the viewpoint of SEU caused by neutrons, it is considered that Antifuse = Flash >> SRAM.

Next, why are Flash-based FPGAs resistant to soft errors? I would like to introduce about

Why is it resistant to soft errors?

There are two main reasons why Microchip FPGAs are resistant to soft errors:

- Resistance due to the built-in structure

- Resistant with Flash-based technology

First, I will explain from 1.

1. Resistance due to the built-in structure

Here we introduce the structure of the Flash-based FPGA.

A typical flash memory holds the data itself in Flash cells. For example, in the case of the MLC (Multi Level Cell) method, it holds 4 values from 11 to 00.

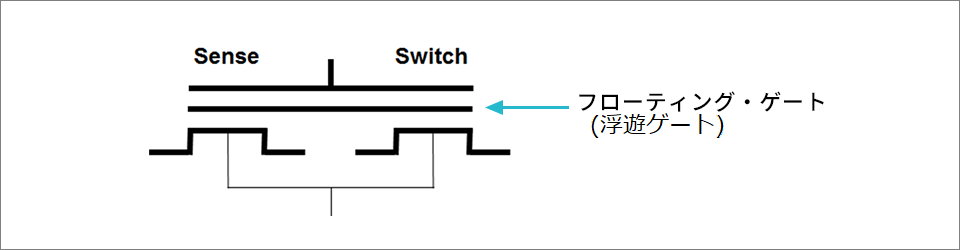

On the other hand, the FPGA's Flash cell functions as a wiring structure switch unlike the Flash cell of general flash memory. Below is a representative example of a Microchip FPGA Flash cell structure.

Unlike general flash memory, it has a so-called 2T type flash structure that shares the floating gate and has a physical size. The Flash cell on the “Sense” side plays the role of programming (writing). On the other hand, the Flash cell on the “Switch” side plays the role of logic operation (wiring switch).

Including the above, Flash-based FPGAs incorporate the following structural innovations to significantly improve reliability.

- Floating gate shared by Sense and Switch to store 10x more charge

- thick tunnel oxide

- Program (write) count limit

Next, we will explain 2.

2. Tolerance with Flash-based technology

As you know, a flash cell is programmed with “0” and “1” by charging/discharging the floating gate with Erase (charge) and Program (discharge) as one cycle. Erase and Program operations are normally performed at very high voltages.

Generally, the energy generated by SEU is thought to be around 5V, and considering the high voltage of Flash-based FPGA Erase and Program, the impact of 5V can be said to be almost negligible. In this way, Flash-based FPGA technology can be said to be ideally resistant to SEUs.

Summary

The reasons why Microchip's FPGA is resistant to soft errors are as follows.

1. Resistance due to the built-in structure

- Floating gate shared by Sense and Switch to store 10x more charge

- thick tunnel oxide

- Program (write) count limit

2. Tolerance with Flash-based technology

Furthermore, being strong against soft errors has the following advantages.

- Reduce man-hours for soft error analysis and countermeasures

- Improved reliability

The above is [Why is it strong against soft errors? 】was.

Inquiry

If you have any questions regarding this article, please contact us below.