A must for printer designers! Summary of added value in low consumption small FPGA

In this article, we will introduce a solution using Lattice's low power consumption and small FPGA for those who are designing printers.

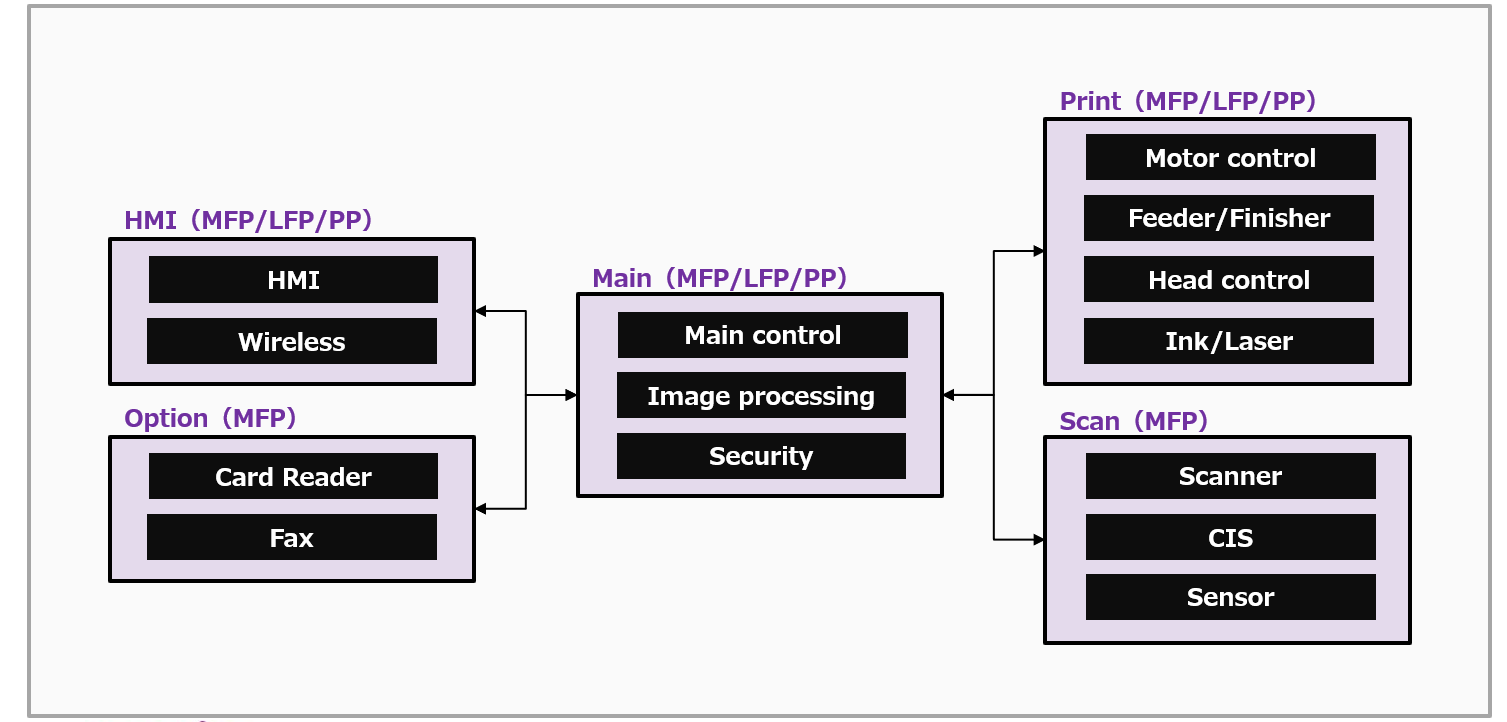

The configuration of the printer is roughly as follows,

I. Main processing unit

Ⅱ. Print section

Ⅲ. Scan part

Ⅳ.HMI section

Ⅴ. Options

We will introduce the optimal solution for each functional block separately, so please take a look at what you are currently designing!

I. Main processing unit

In the main processing section, we will introduce the following three solutions.

1. Power monitoring and power sequence control with a small FPGA for SoCs and CPUs that require power sequence management

2. IO expansion and level shift with small FPGA for ASIC and CPU lacking IO due to bus connection etc.

3. For boards that require security support such as NIST, build a Secure boot configuration with a small FPGA with a security engine installed as hardware.

Ⅰ-1. Power monitoring and power sequence control

・Contributes to the reduction of the board area by integrating the power supply monitoring mechanism with a discrete circuit into an IC.

・It has 6 to 12 channels of multi-power monitoring ports, 368 trip point settings, and high-precision monitoring in units of 15 to 20 mv.

・It is possible to detect power supply anomalies and their signs, and record the details for use in failure analysis.

Ⅰ-2. IO Expansion/Level Shift

・Compact, low-power, low-cost FPGA solves ASIC and CPU port shortages

・Adjust the voltage level between ICs that do not match the voltage level

・At Lattice, it can be realized collectively with a 1-chip type FPGA with built-in Flash that can be driven by a single 3.3V power supply.

Ⅰ-3. Secure boot with a small FPGA equipped with a security engine as hardware

Realize the following functions required by NIST 800-193 with a small FPGA

・Protection: Sign configuration data

・Detection: XO3D verifies the signature

・Recovery: After verification, start booting from another flash if there is a problem

↓↓↓Details can be downloaded from the bottom of the page↓↓↓

Ⅱ. Print section

In the printing department, we will introduce the following five solutions.

1. Multi-axis synchronous control of Stepping Mmotor

2. Servo motor FOC control

3. Head board control and ADC

4. Communication between multiple boards such as Ink/Laser boards

5. Reduced wiring for inter-board communication cables

Ⅱ-1. Multi-axis synchronous control of Stepping Mmotor

High precision control of multiple axes with 1 chip by outputting PWM by taking advantage of the parallel processing capability of FPGA

II-2. Servo motor FOC control

・Accuracy can be improved by leaving the current loop calculation from the MCU to the FPGA

・Provide libraries such as Park conversion and Clarke conversion

・Integration of encoder I/F and filter circuits can be implemented together

・Lattice can realize these processes in a minimum 10mm square package.

Ⅱ-3. Head board control and ADC

・Simultaneously control multiple head boards while suppressing heat generation with a small, low power consumption FPGA

・Monitor analog signal of temperature sensor with built-in ADC

Ⅱ-4. Communication between multiple substrates such as ink/laser substrates

・Flexible response to requests such as terminal board expansion with low cost and small FPGA

・It is possible to incorporate functions such as logic IC integration and IO expansion as an aid to the MCU on the board.

・Ether-connect reference design available from Lattice

Ⅱ-5. Reducing wiring for inter-board communication cables

・Wiring is reduced by eliminating the LVDS Clock Lane and performing communication.

・Skew between Data/Clock does not occur

↓↓↓Details can be downloaded from the bottom of the page↓↓↓

Ⅲ. Scan part

In the scanning department, we will introduce the following two solutions.

1. Summary of Sensor IF

2. Summary of Channel Link

III-1. Summary of Sensor IF

・Integrate multiple channels of I2C, UART, and GPIO and send and receive with a single wire

・Up to 7 channels can be combined (total data rate is 7.5 Mbps or less)

・I2C supports 100Kbps, 400Kbps [Fast-Mode], 1Mbps [Fast-Mode Plus]

- GPIO can transmit and receive up to 16bit and 2Mbps per channel

III-2. Summary of Channel Link

・Channel Link output from CCD and CIS image sensors via AFE can be received by a small, low-power FPGA.

・Hard macro enables 1:7 Deserialization with 1 chip

↓↓↓Details can be downloaded from the bottom of the page↓↓↓

Ⅳ.HMI section

The HMI Department will introduce the following two solutions.

1. Summary of video IF

2. Summary of Wifi Module IF

Ⅳ-1. Summary of Video IF

・Display IF (FPD Link and MIPI DSI) conversion and transmission to the main board with SerDes (PCIe and eDP)

・Lattice can be realized with a minimum 10x10mm FPGA

Ⅳ-2. Summary of Wifi Module IF

CPU load can be reduced by using a small, low-power FPGA to control PCIe and process data on the CPU.

↓↓↓Details can be downloaded from the bottom of the page↓↓↓

Ⅴ.Option section

In the Options section, we will introduce the following two solutions.

1. Summary of logic ICs

2. Utilization of Edge AI

V-1. Summary of Logic ICs

Collectively control multiple Sensor IFs used in FAX and card readers

・It is possible to perform gesture detection, voice recognition, and human detection by AI processing with a small FPGA.

・Realized by overwhelmingly low power consumption AI solution by Lattice FPGA

Related Information

Document download

For those who want to know the specific product names and package lineup that can realize these solutions, detailed information is provided in the following materials. Please take a look at it!

Inquiry

If you have any questions regarding this article, please contact us below.

Various information list

If you are interested in Lattice-related technical information, seminar information, FAQ, etc., please click below.