The Intel® Stratix® V GT Transceiver Signal Integrity (SI) Development Kit provides a platform for electrical compliance testing and interconnectivity analysis. With access to multiple channels, designers can use SMA connectors and industry-favorite backplane connectors for real-world system analysis. With this development kit, you can:

feature

- Evaluate transceiver link performance up to 28 Gbps

- Generate and check pseudo-random binary sequence (PRBS) patterns with an easy-to-use GUI (no Quartus ® II development software required)

- Fine tune link settings for optimal bit error ratio (BER) with advanced equalization capabilities

- Performing Jitter Analysis

- The Stratix V GT FPGA physical medium attachment (PMA) supports target protocols (CEI-25/28G, CEI-11G, PCI Express ® (PCIe ®) Gen 3.0, 10GBASE-KR, 10 Gigabit Ethernet, XAUI, CEI-6G, Serial RapidIO ®, HD-SDI, etc.)

- Evaluate custom backplane performance and link BER using high speed backplane connectors

Order information

| product name | Transceiver Signal Integrity Development Kit, Stratix V GT Edition |

| order code | DK-SI-5SGTMC7N |

Contents of the development kit

The Transceiver SI Development Kit, Stratix V GT Edition features:

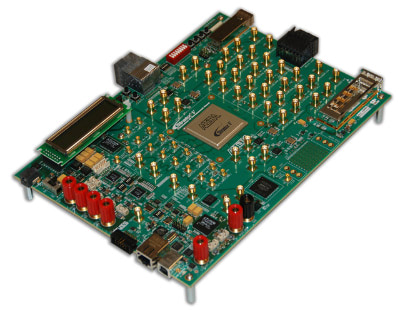

- Stratix V GT development board (see Figure 1)

- On-board device

- 5SGTMC7K3F40C2N

- Configuration status and setup elements

- JTAG

- Onboard USB-Blaster™

- Fast Passive Parallel (FPP) configuration via MAX ® II devices and flash memory

- Can store two configuration files

- Temperature measurement circuit (die and ambient temperature)

- clock

- 50 MHz, 125 MHz, programmable oscillator (preset values: 624 MHz, 644.5 MHz, 706.25 MHz, 875 MHz)

- SMA connector for supplying an external differential clock to the transceiver reference clock

- SMA connector for feeding an external differential clock to the FPGA fabric

- SMA connectors for outputting a differential clock from the FPGA's Phase-Locked Loop (PLL) output pins

- General purpose user input/output

- 10/100/1000 Mbps Ethernet PHY (RGMII) with RJ-45 (copper) connector

- 16x2 character LCD

- One 8-position DIP switch

- 8 user LEDs

- 4 user push buttons

- memory device

- 128 megabytes (MB) synchronous flash memory (primarily used to store FPGA configuration)

- High speed serial interface

- Four full-duplex GTB (28.05 Gbps) transceiver channels routed to MMPX connectors

- 7 full-duplex GXB (12.5 Gbps) transceiver channels routed to SMA connectors

- short traces on micro strip

- Six stripline channels from the same transceiver block (all trace lengths match between channels)

- 21 full-duplex GXB transceiver channels routed to backplane connectors

- 7 channels to Molex ® Impact ® connectors

- 7 channels to Amphenol ® XCede ®

- 7 channels to Tyco Strada ® Whisper ® connector footprint (connector not mounted)

- power consumption

- Laptop DC power input

- Voltage adjustment function

- On-board device

- Stratix V GT Transceiver SI Development Kit Software Contents

- Intel's complete design suite (download from Download Center)

- Quartus II Development Software Supports Stratix V FPGAs

- 1 year license included

- Nios ® II Embedded Design Suite

- MegaCore ® IP library including PCI Express, triple-speed Ethernet, serial digital interface (SDI), and DDR3 SDRAM high-performance controller MegaCore IP cores

- IP evaluation via OpenCore Plus also available

- Board Update Portal

- Equipped with Nios II web server and remote system updates

- GUI based board test system

- Interface to PC via JTAG

- User controllable PMA settings (pre-emphasis, equalization, etc.)

- Status display (error, BER, etc.)

- User guide

- Reference manual

- Board schematic and layout design files

- Intel's complete design suite (download from Download Center)

Figure 1. Stratix V GT Transceiver Signal Integrity Development Kit

Related Documents

| document | explanation |

| Transceiver Signal Integrity Development Kit, Stratix V GT Edition User Guide (PDF) | Describes how to set up the Transceiver SI Development Kit and use the included software. |

| Transceiver Signal Integrity Development Kit, Stratix V GT Edition Reference Manual (English, PDF) | Contains details about the board's components and interfaces. |

| kit installation (For ES silicon board) |

Full installation of all files included in the development kit including reference manuals, user guides, quick start guides, bill of materials, layouts, PCBs, schematics, board update portal example files, etc. |