Hello

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

Defect situation

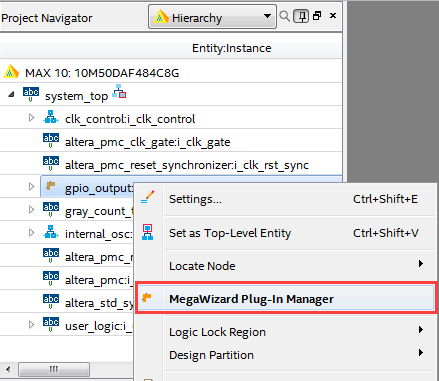

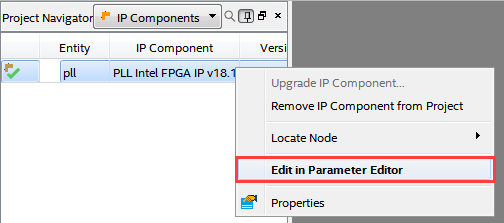

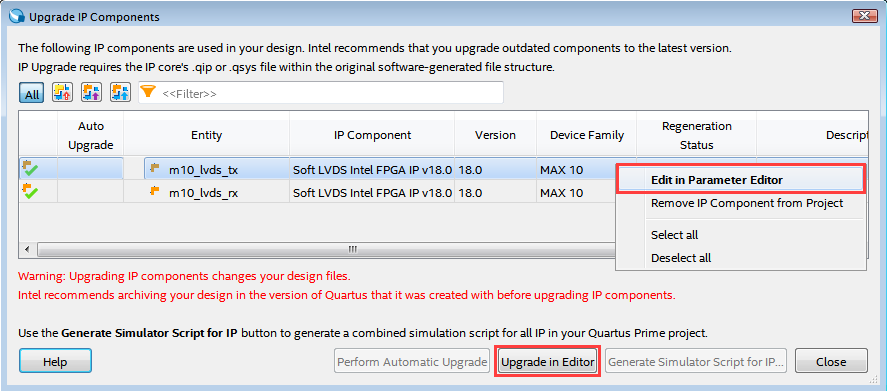

After creating an IP module from Quartus Prime's IP catalog, if you need to change (update) the IP's parameters, either of the following will launch the parameters screen and enter Edit mode, right?

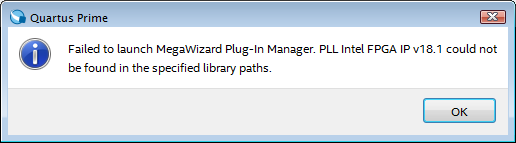

For some IPs, even though I tried to update the IP or edit it with the same version as the one I created, in any flow the following message (Fail to launch MegaWizard Plug-In Manager.) appears and the editor crashes. It may not start!

(*Depending on the IP, there are things that do not say anything without even showing a message.)

This is a bug in Quartus Prime 18.0 and 18.1. (Some IPs have been improved in 18.1.)

It will be fixed in a future release, but until then please use this workaround.

ワークアラウンド(回避策)

For example, if you try to edit the PLL Intel FPGA IP created in ver.18.1 and the parameter screen does not start with the message Fail to launch~, edit the pll_wizard.lst file as follows.

① Open <quartus_prime_18.1_install_dir>\ip\altera\altera_pll\pll_wizard.lst in a text editor.

② Change the IP name in ver.18.1 to PLL Intel FPGA IP.

For example:

[Basic Functions|Clocks; PLLs and Resets|PLL] Altera PLL v18.1= "%t" "%w/../common/lib/megawizard.pl" --wizard:altera_pll --early_gen:on --wizard_file:"%w/source/top/pll_hw.tcl" --familyparameter:device_family %f %o %h <INFO> <QIP_FILE_ENABLED/> <ACCEPT_OTHER_CNX VALUE="ON"/> <DEVICE_FAMILY SUPPORTED="NONE | Stratix V | Arria V | Cyclone V | Arria V GZ" SUPPORT_CHECK="ON" /> <LANGUAGES AHDL="OFF"/> <PINPLAN SUPPORTED="ON"/> <ALIAS>Altera PLL</ALIAS> <ALIAS>Altera PLL v10.0</ALIAS> <ALIAS>Altera PLL v10.1</ALIAS> <ALIAS>Altera PLL v11.0</ALIAS> <ALIAS>Altera PLL v11.1</ALIAS> <ALIAS>Altera PLL v12.0</ALIAS> <ALIAS>Altera PLL v12.1</ALIAS> <ALIAS>Altera PLL v13.0</ALIAS> <ALIAS>Altera PLL v13.1</ALIAS> <ALIAS>Altera PLL v14.0</ALIAS> <ALIAS>Altera PLL v14.1</ALIAS> <ALIAS>Altera PLL v15.0</ALIAS> <ALIAS>Altera PLL v15.1</ALIAS> <ALIAS>Altera PLL v16.0</ALIAS> <ALIAS>Altera PLL v16.1</ALIAS> <ALIAS>Altera PLL v17.0</ALIAS> <ALIAS>Altera PLL v17.1</ALIAS> <ALIAS>Altera PLL v18.0</ALIAS> <ALIAS>PLL Intel FPGA IP v18.1</ALIAS> <ALIAS>Altera PLL v19.0</ALIAS> <ALIAS>Altera PLL v19.1</ALIAS> <ALIAS>Altera PLL v20.0</ALIAS> <ALIAS>Altera PLL v20.1</ALIAS> </INFO>③ Save the pll_wizard.lst file.

This will launch the parameter screen of the PLL Intel FPGA IP.

If the IP created with ver.18.0 (including those with this workaround) did not launch with Fail to launch MegaWizard Plug-In Manager. when editing with ver.18.1, In *_wizard.lst, the ver.18.0 line also needs to be modified.

例) ... <ALIAS>Altera PLL v17.1</ALIAS> <ALIAS>PLL Intel FPGA IP v18.0</ALIAS> <ALIAS>PLL Intel FPGA IP v18.1</ALIAS> ...

This bug is due to IP names being renamed in Quartus Prim 18.0 and later.

Although there are many IPs that have been successfully renamed, some IPs are incomplete and this problem is occurring.

For example, the following IPs apply:

|

old IP name |

IP name after ver.18.0 |

| Altera GPIO Lite | GPIO Lite Intel FPGA IP |

| ALTERA_MULT_ADD | Multiply Adder Intel FPGA IP |

| Altera PLL | PLL Intel FPGA IP |

| Altera PLL Reconfig | PLL Reconfig Intel FPGA IP |

| Altera Soft LVDS | Soft LVDS Intel FPGA IP |

| Altera Unique Chip ID | Unique Chip ID Intel FPGA IP |

| Triple-Speed Ethernet | Triple-Speed Ethernet Intel FPGA IP |

| Such | Such |

|

old IP name |

IP name after ver.18.1 |

| ALTERA_FP_FUNCTIONS | FP_FUNCTIONS Intel FPGA IP |

| Such | Such |

Edit some contents of the *.lst files (see below) for these IPs to the new IP names for ver.18.0 or later.

The *.lst files for the above IP are present in the path below.

|

IP name after ver.18.0 |

*.lst file path |

| GPIO Lite Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altera_gpio_lite\altera_gpio_lite_wizard.lst |

| Multiply Adder Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altera_mult_add\altera_mult_add_wizard.lst |

| PLL Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altera_pll\pll_wizard.lst |

| PLL Reconfig Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altera_pll_reconfig\pll_reconfig_wizard.lst |

| Soft LVDS Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altera_soft_lvds\altera_soft_lvds_wizard.lst |

| Unique Chip ID Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\altchip_id\altchip_id_wizard.lst |

| Triple-Speed Ethernet Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\ethernet\altera_eth_tse\altera_eth_tse_wizard.lst |

| Such | - |

|

IP name after ver.18.1 |

*.lst file path |

| FP_FUNCTIONS Intel FPGA IP | <quartus_prime_install_dir>\ip\altera\dsp\altera_fp_functions\altera_fp_wizard.lst |

| Such | - |

* "etc" is because there is an unconfirmed IP. We will update the information as soon as it is confirmed.

Until it's fixed, this workaround will get you through it!

thank you.