Even though the device was designed and evaluated in the most natural way and shipped, if it was connected to other devices and operated, it would "malfunction sometimes" or "malfunction" in the heat of the summer. I sometimes hear people say, “I do.” Most of these causes are affected by timing, and are caused by input signals that are not synchronized with the system (asynchronous input signals) and hazards that occur on the circuit.

Therefore, in this article, I will explain the effects of input signals that are not synchronized with the system and how to solve them.

Learn more about how hazards affect your system.

[A Must-See for RTL Design Beginners] Effects of Hazard Signals on Systems

asynchronous input

Meaning of asynchronous input

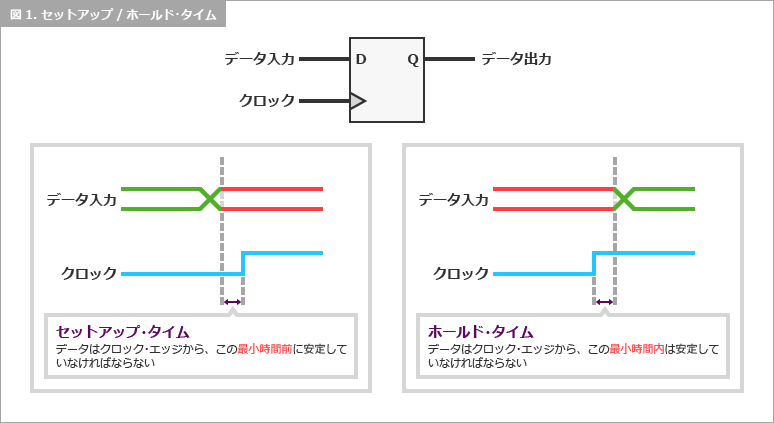

In FPGA, there are requirements for setup time (t SU) and hold time (t H) between the flip-flop input signal and the clock signal to ensure stable operation. Digital logic designers must strictly adhere to these regulations. This requirement is stored in the development software provided by the FPGA manufacturer. Figure 1 shows a conceptual diagram of setup time and hold time.

Violation of this setup/hold time specification can result in temporary instability called "metastability" or a state that differs from the system-defined state. This factor greatly affects the reliability of the system. When data is exchanged between different devices, it becomes an asynchronous system, and it is not possible to guarantee the setup time and hold time specifications between the received signal and the system clock. Synchronization of signals is required when sending and receiving signals between these devices, and metastability is likely to occur if this synchronization is not performed. (Metastability does not always occur. And even if it does occur, the time is usually on the order of ns, so it may not be a problem. However, although the probability is extremely low, metastable instability It may take a long time.)

What is Metastable

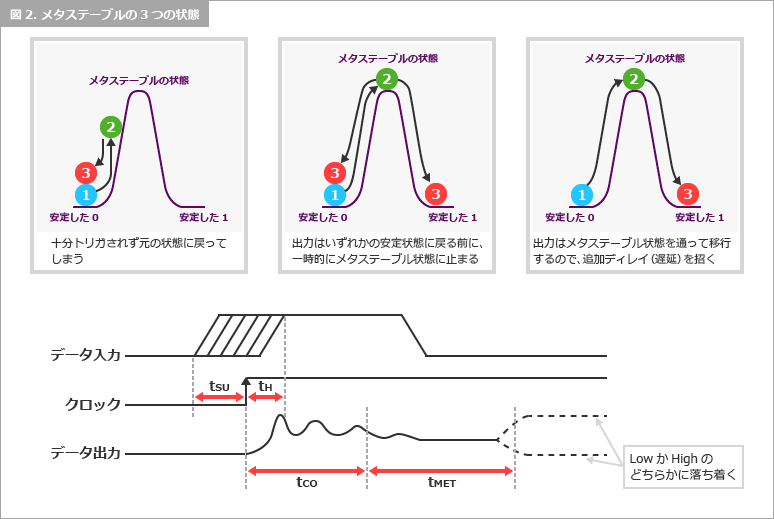

Metastable refers to a state in which the output state is not stable even after the originally specified clock output time t CO is exceeded. The time required for stabilization, t MET, depends on the ambient conditions and device manufacturing technology.

The operation of the register can be compared to the state in which a ball moves along a single mountain without friction, as shown in Figure 2. Each side of the mountain represents a stable state (High or Low), and the top of the mountain represents a metastable state.

If the input to the flip-flop meets the specified minimum setup time tSU and hold time tH, the output will transition from one stable state to the other (high to low, or from Low to High) with no additional delay.

On the other hand, if the data input to the flip-flop violates the stipulated setup time or hold time stipulations, the flip-flop will not be fully triggered and the output will be doubled within the stipulated time. It may not transition to one of the stable states immediately. This improper triggering can cause the output to glitch or temporarily metastable between a high and low state, causing the output to take longer to return to a stable state. Even under these conditions, the time from clock transition to output stabilization will increase.

Metastability does not necessarily make system performance unpredictable. As long as the flip-flop can be allowed to wait long enough to return to a stable state, this does not affect system performance and even if the output of the flip-flop is temporarily undefined, this A signal can return to a stable state before it is actually used. Therefore, by allowing additional time t MET for the signal to settle to a prespecified value, an unspecified signal can be avoided from propagating to other parts of the system. Masu.

System impact of metastability

As I said earlier, asynchronous inputs are bad for your system. Basically, once the flip-flops in the system become metastable, they become not only unstable, but in the worst case system hangs. There is no way to recover other than turning off the power. In this way, the state of metastability cannot be defined artificially from the system. Only the physical properties of the semiconductor can control the state. It's "God only knows".

A particularly vulnerable example is the case of identical clock systems. For example, sending and receiving signals between devices that operate on a 50MHz master oscillator. Even though they are nominally the same frequency, the two master oscillators have different frequency deviations and temperature coefficients, resulting in subtle frequency fluctuations. As a result, the signals are asynchronous to each other. please note.

Workaround for metastability

The two most common ways to reduce the effects of metastability are:

・ Use a synchronous flip-flop

・ Use FIFO logic

I will briefly explain these.

Using Synchronous Flip-Flops

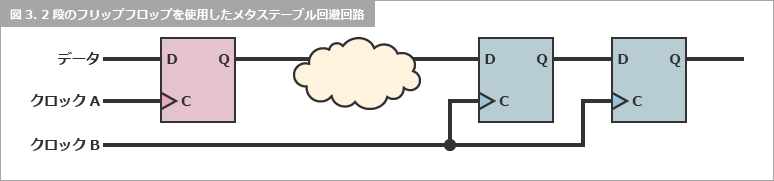

A common metastability countermeasure is to insert multiple synchronizing flip-flops in the receiving side clock domain at the later stages, as shown in Figure 3, in order to synchronize the asynchronous input signal with the system clock. However, although the number of inserted flip-flops greatly improves the reliability of the system, the latency of the system increases by the number of inserted flip-flops, which may cause the performance of the entire system to deteriorate. there is.

If the difference between the repetition frequency of the asynchronous input signal and the frequency of the system clock is negligible, one stage is sufficient, but if the two frequencies are adjacent to each other, several stages may be used. You can find out how many stages to insert by checking the MTBF (mean time between failures) with the TimeQuest timing analyzer function of Quartus® Prime. In addition, it is recommended to shorten the FF interval on the receiving side so as to shorten the metastable period.

In Figure 3, even if the synchronizing flip-flop (the preceding flip-flop) produces a metastable output, then the metastable signal may stabilize before the second flip-flop is triggered. This method does not guarantee that the second flip-flop will not trigger an unstable output, but it does improve the probability that the data will be in a valid state before reaching the rest of the circuit. In this way, the number of stages of flip-flops to be inserted is determined based on the reliability required for the system.

In any case, do not feed more than one flip-flop with a single asynchronous input. Feeding a single asynchronous input to multiple flip-flops increases the probability of system error due to metastable conditions. This is because when an asynchronous input signal is input to multiple flip-flops, it is possible that each connected flip-flop will be in a different state, making it impossible to define a unique state in the system. In such a case, insert a synchronizing flip-flop and supply the output after defining a unique state for the system to the subsequent flip-flop or logic.

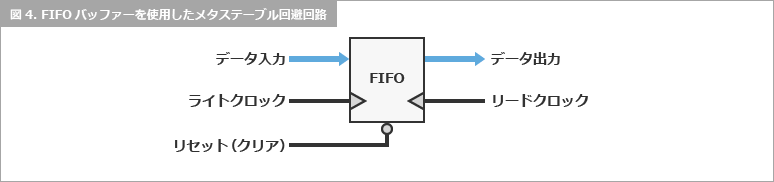

Using FIFO Logic

First-In First-Out (FIFO) logic is used to simultaneously synchronize multiple bits of input such as a data bus. FIFO logic uses synchronizers to pass control signals between two clocks, and data is read/written to dual-port memory. Figure 4 shows the schematic diagram.

At the end

When asynchronous signals enter a system, the system enters an unpredictable state known as metastability. In the worst case, it may cause the system to hang and not recover until the power is turned off. Metastable conditions can occur in the case of signal transfers between devices that are not synchronized throughout the system. Therefore, it is recommended to scrutinize the signal lineage of the entire system, construct a synchronization system, and remove unstable elements.

Click here for recommended articles/materials

[A must-see for RTL design beginners] Differences between synchronous and asynchronous design

[A Must-See for RTL Design Beginners] Effects of Hazard Signals on Systems

Operating characteristics of FPGA/CPLD