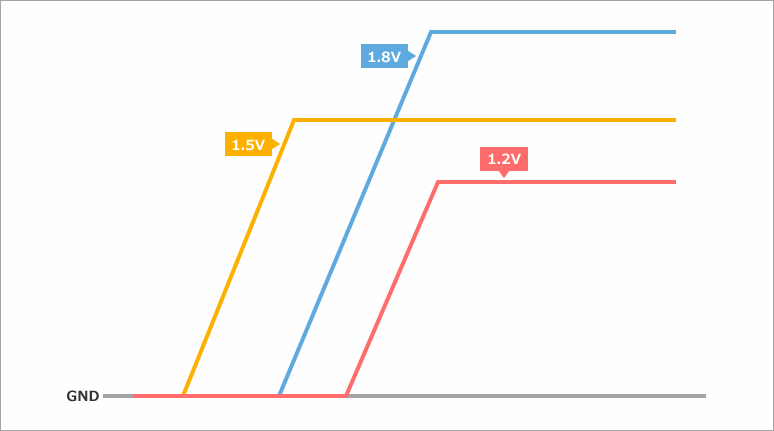

Many semiconductor devices such as FPGAs require multiple power supplies.

At that time, since it is required to keep the power supply sequence, a power supply on/off control pin and output capacitor discharge function may be required.

This time, we will focus on four points to note when using LDOs.

An on/off function is essential for creating a sequence

Modern FPGAs and DSPs generally require a power on/off sequence. In order to control on/off, the power supply IC (module) needs an enable pin for on/off control.

Inexpensive LDOs may not have pins for on/off control, so care must be taken when selecting one.

Rise time control

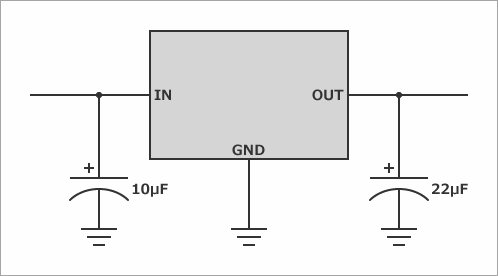

A soft-start feature allows for control of the rise time. However, there are few LDO products that have a soft-start function.

As a countermeasure, it becomes necessary to control the rise time with the capacitance of the output capacitor. However, if too large a capacitor is attached, it will cause a problem at the time of power-down.

Power down sequence

The rules for start-up sequences are well known. However, not much attention has been paid to the fall sequence so far.

Recently, the number of power supplies mounted on a board is increasing, and there are cases where rush current flows if the sequence at the time of shutdown is not carefully considered, so it is important to pay close attention to the shutdown sequence as well.

See this article for why you need a sequence.

No need for power sequencing?

Because of the rise sequence, adjusting the LDO output capacitor by increasing it is good from the perspective of lengthening the rise time, but the fall time will be longer (the discharge time of the capacitor will be longer), so the fall sequence You have to be careful because it will be disadvantageous to

LDO fall sequence

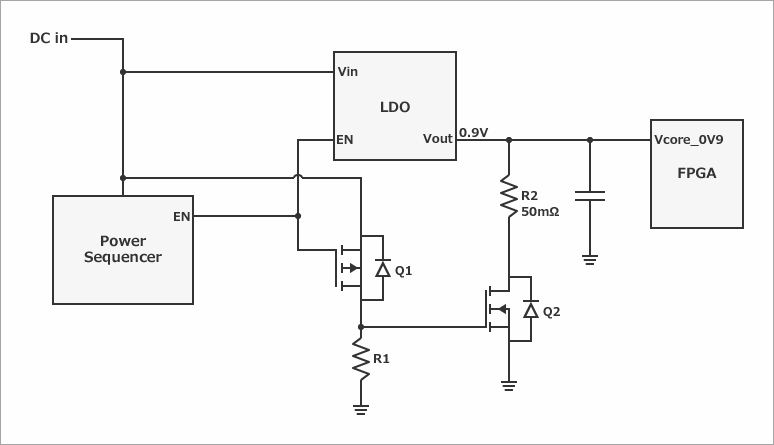

With a switching regulator, if the Low Side FET discharges when it is off, the output voltage will drop immediately, so it is easy to create an off-sequence.

However, most LDOs do not have a discharge function on the output side.

Therefore, start-up sequence control by increasing the output capacitor is not recommended. If it becomes necessary, it is necessary to add an external discharge circuit.

LDO with on/off function and discharge function

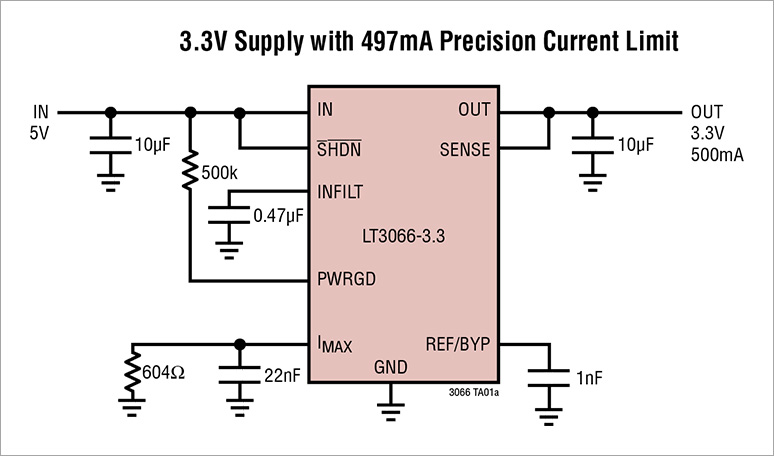

Analog Devices LDOs have an LDO like the LT3066 that has an on/off function (SHDN PIN in Figure 4) and a function to discharge the charge on the output section.

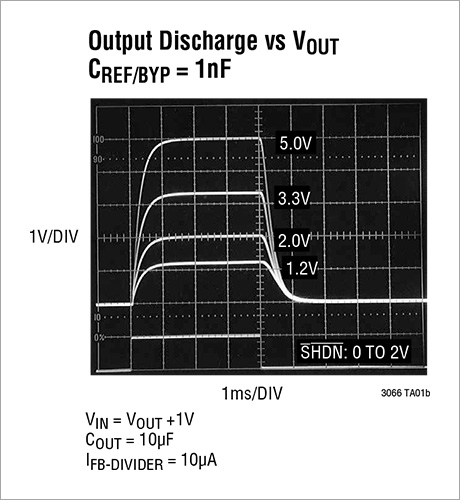

Figure 5 shows the waveform in which the output voltage is quickly reduced to 0V by the output discharge function.

These features allow LDO products to provide clean voltage supplies to PLLs and analog power supplies while performing the power-down sequence required by the FPGA.